Low-temperature test structure of multi-channel high-frequency chip

A low-temperature test, multi-channel technology, applied in the direction of electronic circuit testing, measuring electricity, measuring devices, etc., can solve the problems of not using high frequency, the distance between test points can not be too small, high frequency impedance mismatch, etc., to achieve convenient disassembly and assembly Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0021] The present invention will be further described below in conjunction with specific embodiments. It should be understood that these examples are only used to illustrate the present invention and not to limit the scope of the present invention. In addition, it should be understood that after reading the content taught by the present invention, those skilled in the art can make various changes or modifications to the present invention, and these equivalent forms also fall within the scope defined by the appended claims of the present application.

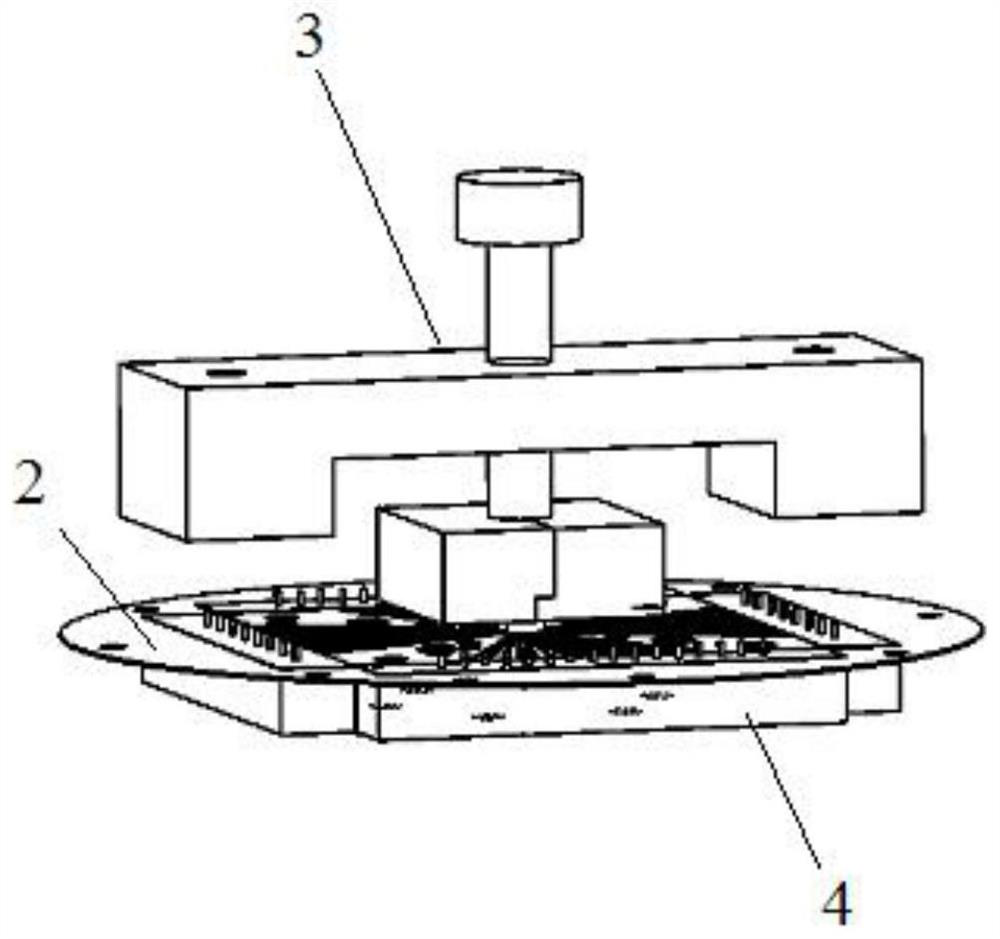

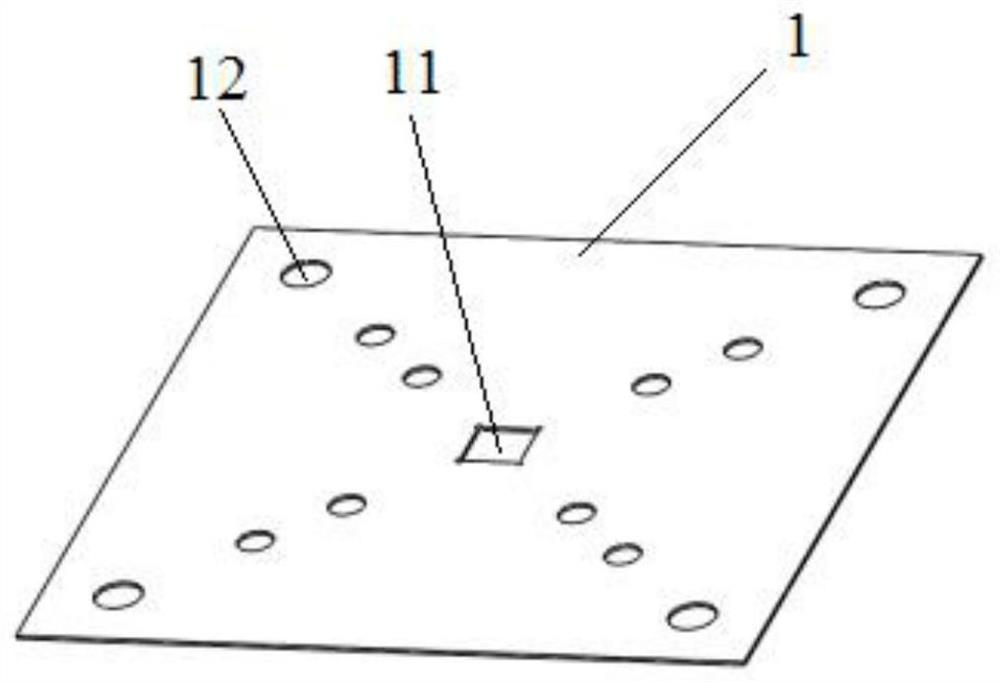

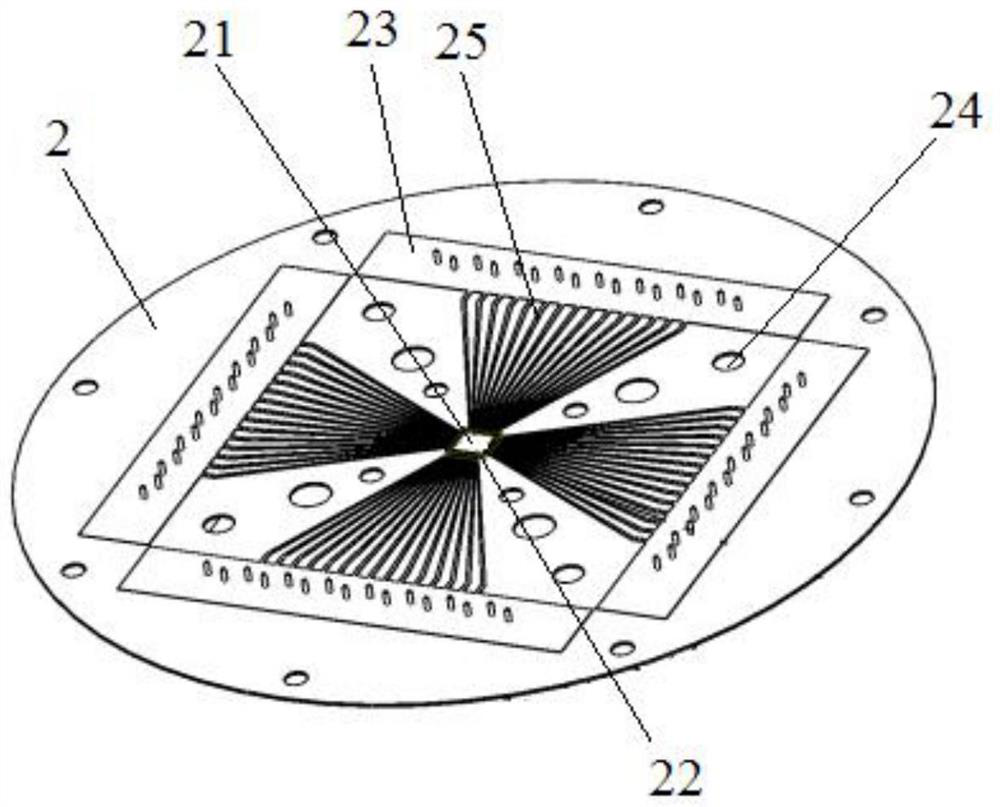

[0022] Embodiments of the present invention relate to a low-temperature test structure of a multi-channel high-frequency chip, such as figure 1 As shown, it includes a chip positioning printed circuit board 1, a multi-channel interface circuit board 2 and a pressure device 3. The chip positioning printed circuit board 1 is used to place the chip to be tested; the multi-channel interface circuit board 2 is provided with There ar...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com