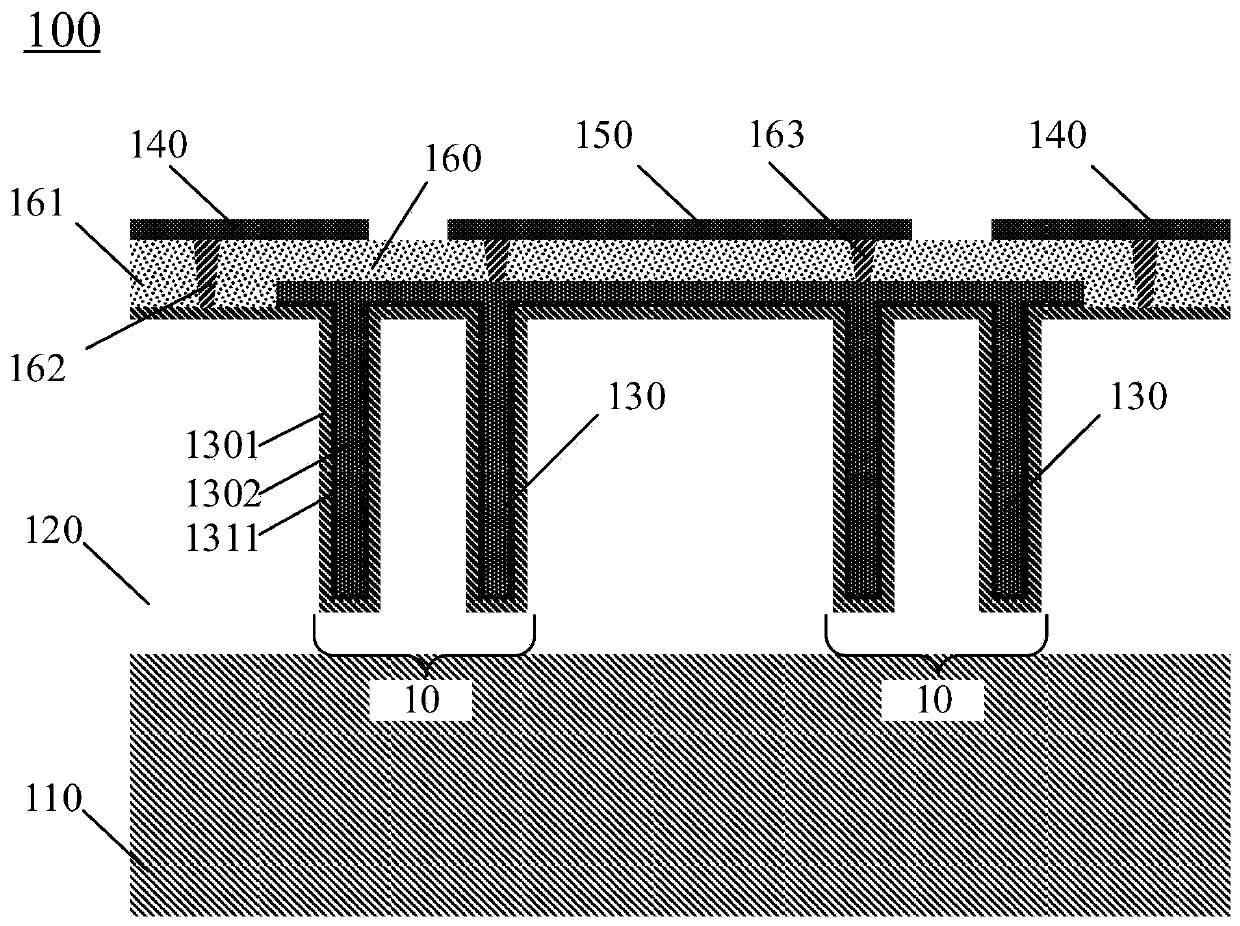

Capacitor and manufacturing method thereof

A capacitor and electrode technology, applied in the field of capacitors, can solve the problems of high price and high cost of silicon wafers, and achieve the effect of reducing unit processing cost and cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

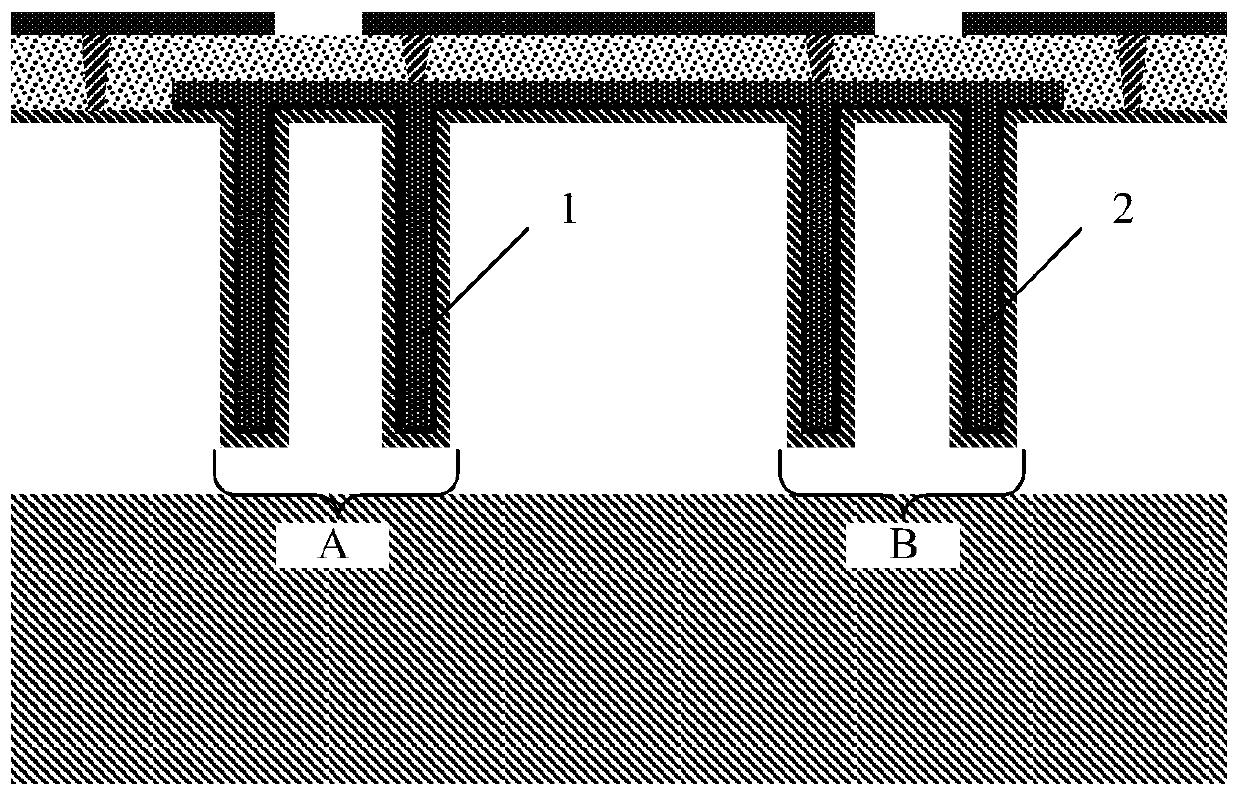

Embodiment 1

[0304] Step 1: Select fused silica glass as the non-semiconductor substrate.

[0305] Step 2: using a plasma enhanced chemical vapor deposition (Plasma Enhanced Chemical Vapor Deposition, PECVD) process to deposit a 10 micron amorphous silicon layer on the non-semiconductor substrate as the first semiconductor layer.

[0306] Step 3: First, use patterning techniques such as photolithography, nanoimprinting, and laser direct writing to form a patterned mask layer on the upper surface of the first semiconductor layer, and then use a deep silicon etching process to form a second mask layer on the first semiconductor layer. A trench array.

[0307] Step 4: Deposit a layer of TiN as the first conductive layer on the trench sidewalls in the first trench array by using the ALD process. If the non-semiconductor substrate is resistant to high temperature, such as fused silica, this step can also use a doping process to form a low-resistivity conductive layer on the sidewalls of the tr...

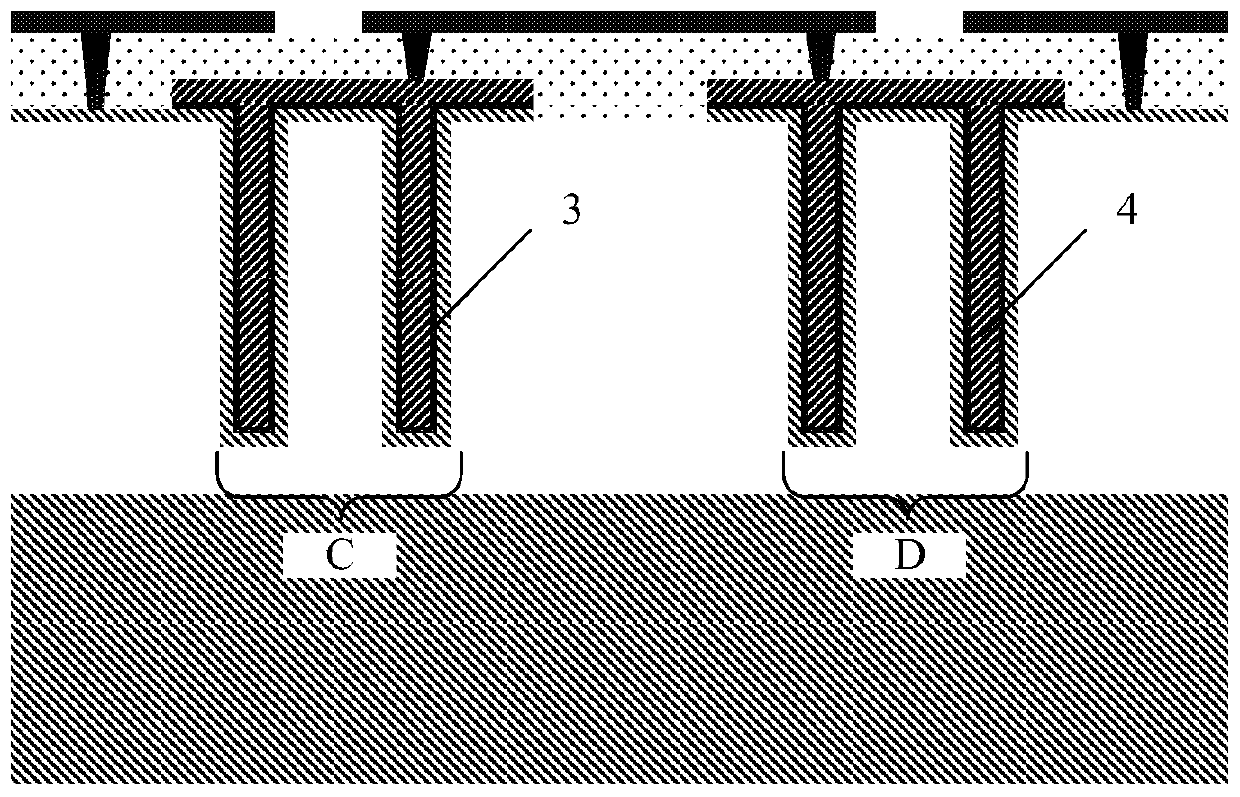

Embodiment 2

[0314] Step 1: Select fused silica glass as the non-semiconductor substrate.

[0315] Step 2: Deposit a 10-micron amorphous silicon layer on the non-semiconductor substrate by PECVD process as the first semiconductor layer.

[0316] Step 3: First, use patterning techniques such as photolithography, nanoimprinting, and laser direct writing to form a mask layer with a pattern on the upper surface of the first semiconductor layer, and then use a deep silicon etching process to form a patterned mask layer on the first semiconductor layer. A first trench array is formed.

[0317] Step 4: Deposit a layer of TiN as the first conductive layer on the trench sidewalls in the first trench array by using the ALD process. If the non-semiconductor substrate is resistant to high temperature, such as fused silica, this step can also use a doping process to form a low-resistivity conductive layer on the sidewalls of the trenches in the first trench array.

[0318] Step 5: Using the ALD proce...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com