Lateral root-enhanced junction field effect transistor device and its preparation method

A field effect transistor and enhancement mode technology, applied in the field of lateral GaN-based enhancement mode junction field effect transistors, can solve the problems of increasing the difficulty of driving circuit design, increasing the off-state loss of power semiconductor devices, etc., to achieve high current output, increase Off-state loss, the effect of simplifying the drive circuit

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

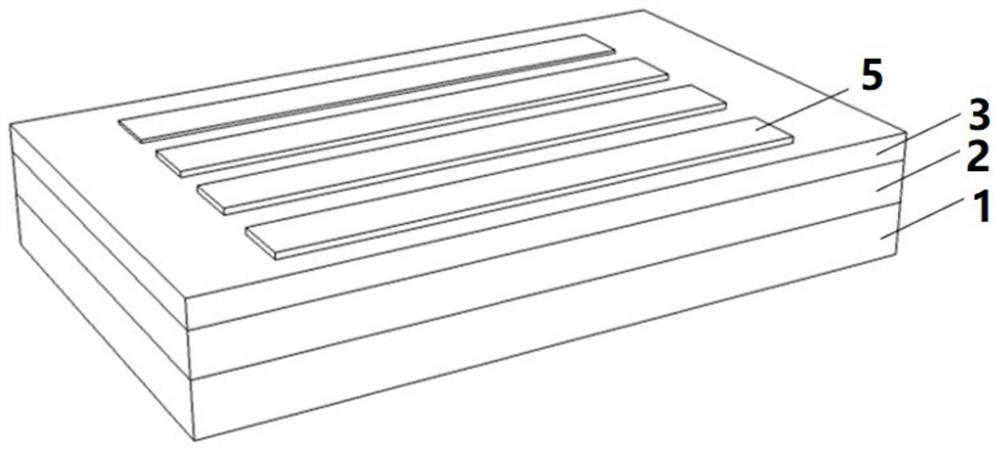

[0041] Such as Figure 1-4 As shown, a method for preparing a lateral GaN-based enhanced junction field effect transistor device, the steps include:

[0042] (1) MOCVD method deposits semi-insulating GaN layer 2 and n-GaN channel layer 3 on the surface of sapphire substrate 1, as figure 1 Shown; growth method of semi-insulating GaN: trimethylgallium and NH 3 As Ga source and N source respectively, the carrier gas is H 2 or N 2 , the growth temperature is 1000-1100°C, and the growth time is 3-5h. The growth method of the n-GaN channel layer: the temperature is 950-1050°C, the silicon doping concentration is 1*10 18 cm -3, growth time 15-20min;

[0043] (2) With the method of ICP chlorine-based plasma etching, etch a plurality of grooves 4 on the n-GaN substrate, the depth of the grooves reaches the semi-insulating GaN layer and overcuts 50-100nm to ensure the is completely removed, as figure 2 shown;

[0044] (3) Use mask selection process, use MOCVD or MBE system to ...

Embodiment 2

[0047] The preparation method of the lateral GaN-based enhancement type junction field effect transistor device is basically the same as that of the first embodiment, the difference is that the p-GaN strip structure is basically flush with the surface of the n-GaN channel layer.

Embodiment 3

[0049] A method for preparing a lateral GaN-based enhanced junction field effect transistor device, the steps comprising:

[0050] (1) MOCVD method deposits semi-insulating GaN layer and n-GaN channel layer on the surface of SiC substrate, the growth method of semi-insulating GaN: trimethylgallium and NH 3 As Ga source and N source respectively, the carrier gas is H 2 or N 2 , the growth temperature is 1000-1100°C, and the growth time is 3-5h. The growth method of the n-GaN channel layer: the temperature is 950-1050°C, the silicon doping concentration is 1*10 18 cm -3 , growth time 15-20min;

[0051] (2) Using ion implantation (the energy of ions is 100-120KeV, and the implantation dose is 1*10 18 cm -3 -1x10 19 cm -3 , annealing at 800-1200 degrees for 30s-60s), injecting multiple pieces of p-GaN with a parallel structure into the n-GaN channel layer to form multiple sandwich p-n junctions;

[0052] (3) Make Ti / Al / Ni / Au30 / 150 / 50 / 150nm multilayer metal on both ends o...

PUM

| Property | Measurement | Unit |

|---|---|---|

| height | aaaaa | aaaaa |

| width | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com