A method for preparing a multi-level fusion three-dimensional system integration structure

A system integration, multi-level technology, applied in the direction of semiconductor/solid-state device parts, semiconductor devices, electrical components, etc., can solve the problems of inability to complete three-dimensional integration, limited integration capabilities, and large volume

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0030] This embodiment provides a method for preparing a multi-level fused three-dimensional system integration structure, including the following steps:

[0031] (1) Make n substrates;

[0032] (2) Welding various electronic devices on the n substrates produced in step (1) to obtain n two-dimensional integrated packaging structures;

[0033] (3) Test n two-dimensional integrated package structures respectively;

[0034] (4) Three-dimensional integrated packaging will be performed on n two-dimensional integrated packaging structures;

[0035] (5) Capping the three-dimensional integrated packaging structure.

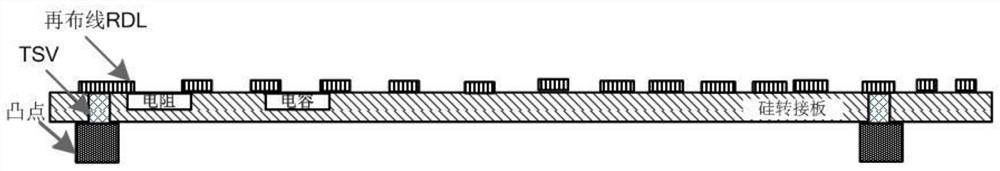

[0036] In the step (1), RDL layers, TSV holes, and bumps are also distributed on the n substrates.

[0037] A cavity is also provided on the substrate, so that corresponding electronic devices can be installed in the cavity.

[0038] In the step (4), the specific process of carrying out three-dimensional integrated packaging on n two-dimensional integrated packaging s...

Embodiment 2

[0043] Using the preparation method of the multi-level fusion three-dimensional system integration structure shown in Example 1 to make a four-layer fusion three-dimensional system integration structure with a basic number of four is as follows:

[0044] (1) Design and manufacture various substrates (such as silicon transfer substrates, ceramic substrates and organic substrates, etc.) according to the design requirements of the distribution, size and electrical connectivity of the bare chip PAD and bumps; Source devices (resistors and capacitors, etc.) to improve the utilization and integration of silicon interposers; design and manufacture cavities on the substrate according to the number, size, thickness and correlation between chips; design and manufacture according to interconnection requirements Redistribute RDL layers, TSVs and bumps, see figure 1 , figure 2 , image 3 ;

[0045] (2) High-precision upside-down welding of various bare chips (such as FPGA chips, CPUs w...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com