A 3D system integration structure with multi-level fusion

A system integration, multi-level technology, applied in the direction of semiconductor/solid-state device parts, semiconductor devices, electrical components, etc., can solve immature, unable to meet the miniaturization of microsystem products, high performance and low power consumption, complex process technology and other issues to achieve cost savings, ensure power integrity, and simplify process methods

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

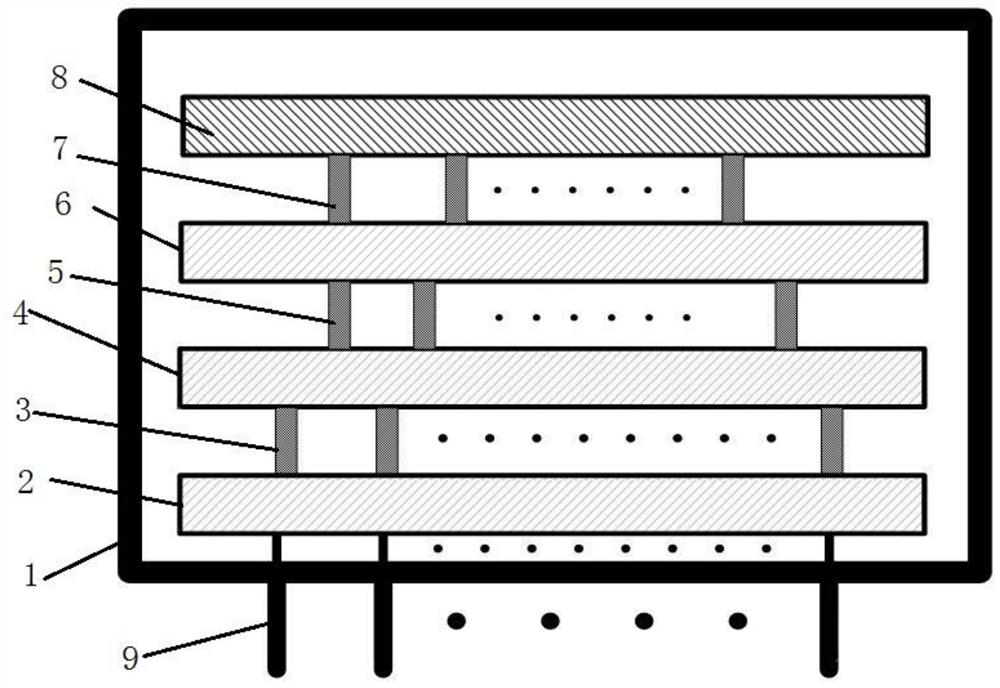

[0021] In order to solve the complex and immature process technology of the existing three-dimensional system integration structure, it cannot meet the requirements of miniaturization, high performance and low power consumption of microsystem products. This embodiment provides a figure 1 The shown multi-level integrated three-dimensional system integration structure includes a shell 1, which is used to protect various chips and devices in the multi-level integrated three-dimensional integrated circuit, providing good airtightness, and facilitating the installation and application of the three-dimensional system integrated structure The bottom surface of the tube shell 1 is provided with a plurality of pins 9, and the tube shell 1 is provided with n sequentially stacked substrate modules, and the n substrate modules are respectively provided with chips and resistance capacitor devices with different functions, so as to realize certain functions, and bumps are provided between t...

Embodiment 2

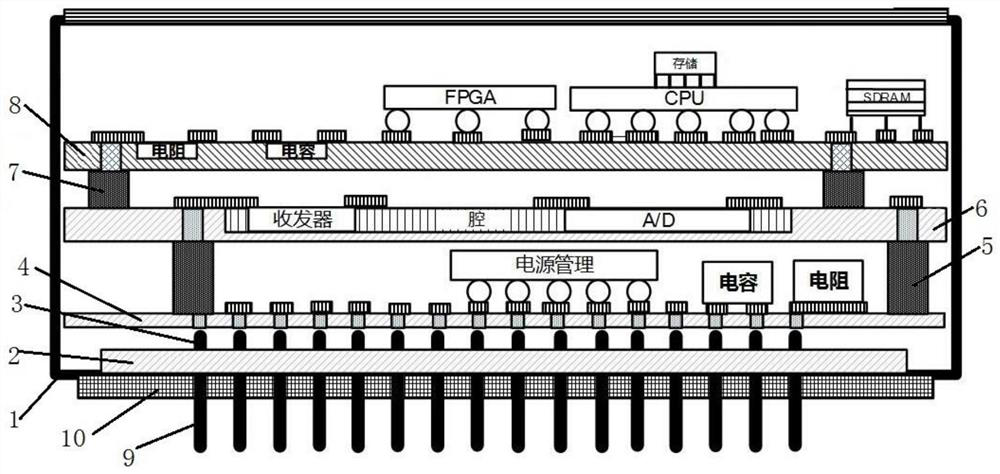

[0023] Such as figure 2 As shown, the tube shell 1 is included, and the main function of the tube shell 1 is to provide corresponding quality assurance for the devices and structures in the multi-level integrated three-dimensional integrated circuit; the bottom surface of the tube shell 1 is provided with a plurality of pins 9, There are three sequentially stacked substrate modules inside the casing 1, which are respectively the first substrate module 2, the second substrate module 4, and the third substrate module 6. The connection between the first substrate module 2 and the second substrate module 4 There is a welding pad 3 between them, and the welding pad 3 (PAD) is electrically connected to the corresponding pin 9 of the package 1, and is used to transfer the corresponding signal line in the second substrate module 4 to the corresponding pin 9 of the package 1, Make the pin arrangement of the three-dimensional integrated circuit meet the requirements of practical applic...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com