A Novel Microwave 3D Integrated System-in-Package Interconnect Structure

A system-level packaging and interconnection structure technology, which is applied in the field of microwave three-dimensional integrated system-level packaging interconnection structure to achieve high processing accuracy, improve integration, and maintain signal integrity.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

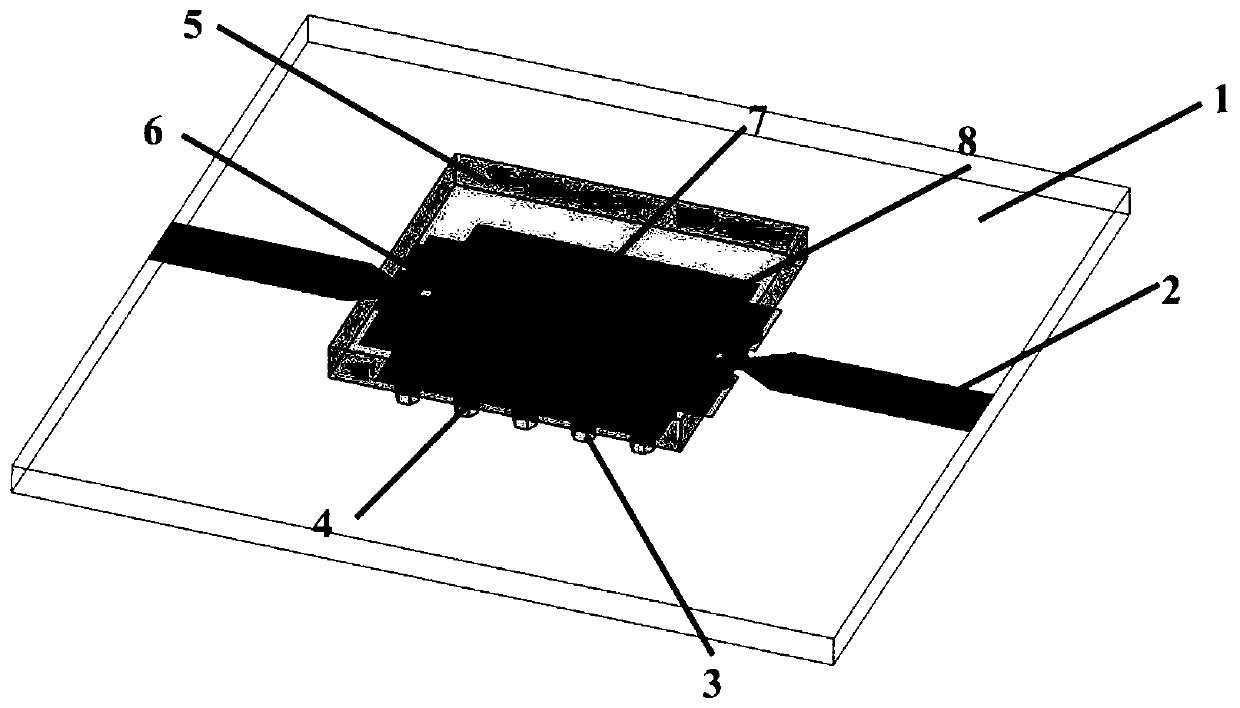

[0020] Such as figure 1 As shown, a microwave three-dimensional integrated system-in-package interconnection structure includes a substrate dielectric substrate 1, a microstrip line 2 on the substrate dielectric substrate, a ground metallization hole array 3 on the substrate dielectric substrate, a gallium arsenide chip 4, Silicon substrate 5, coplanar waveguide transmission line 6 on the silicon substrate, buried cavity 7 opened in the silicon substrate above the sensitive position of the gallium arsenide chip, metallized hole array ground plane metal 8 on the upper surface of the substrate medium; the sensitive position refers to part of the interior lines or active areas.

[0021] The gallium arsenide chip 4 is arranged between the silicon substrate 5 and the ground plane metal 8 , the buried cavity 7 is not penetrated above, and the microstrip line 2 is connected to the gallium arsenide chip 4 through a coplanar waveguide transmission line 6 .

Embodiment 2

[0023] The difference between this embodiment and Embodiment 1 is that a penetrating non-metallized groove is opened above the sensitive position of the gallium arsenide chip.

Embodiment 3

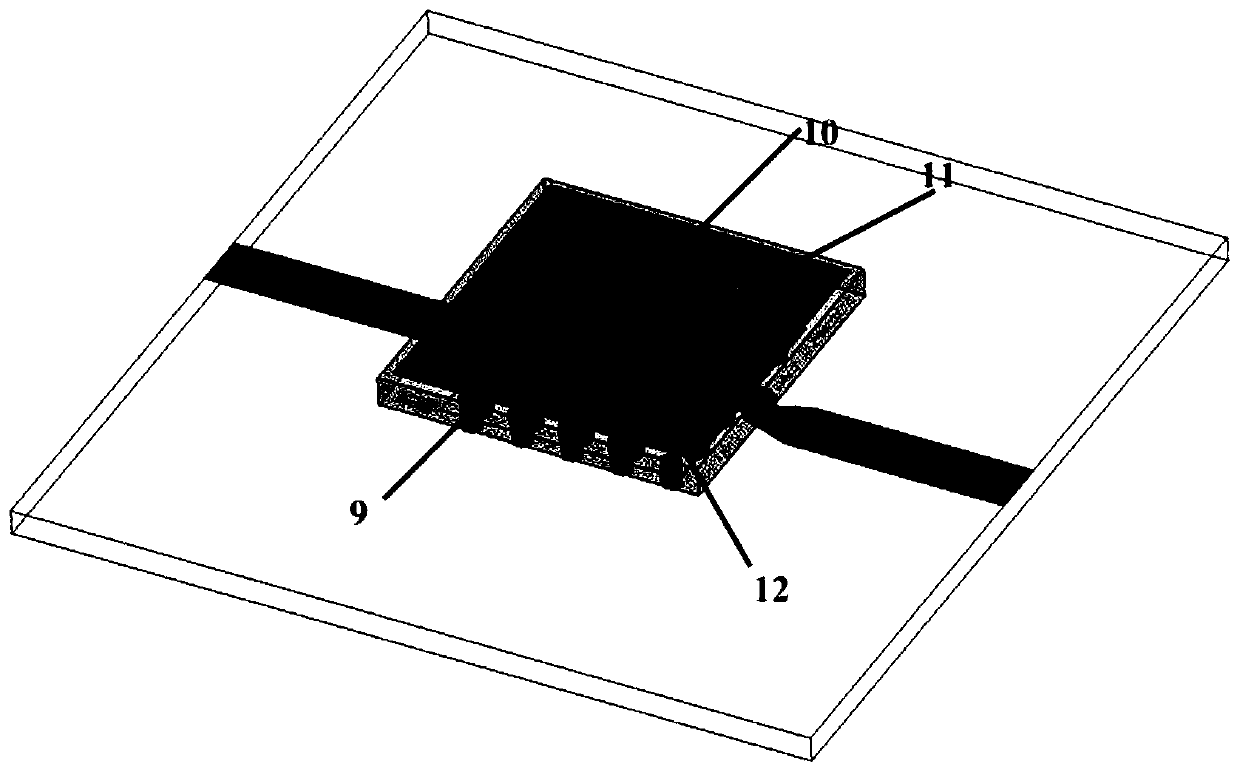

[0025] Such as figure 2 As shown, the difference between this embodiment and Embodiment 1 is that the interconnection structure also includes solder balls 10, through-silicon vias 11 for grounding the microstrip transmission line in the silicon substrate, and a reference ground plane 12 for the microstrip transmission line on the top surface of the silicon substrate. , the solder balls 10 are used to connect the silicon substrate 5 and the ground plane metal 8 .

[0026] The gallium arsenide chip 4 is interconnected with the microstrip transmission line 9 on the silicon substrate through flip-chip, and then the entire vertical interconnection structure is flipped onto the substrate dielectric substrate through solder balls 10, and passes through the microstrip line 2 on the substrate dielectric substrate. Interconnect with other components of the system.

[0027] The manufacturing process is as follows: Flip-chip the gallium arsenide chip 4 onto the silicon substrate 5, and ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com