A double T-shaped gate, and a manufacturing method and an application thereof

A manufacturing method and gate foot technology, applied to electrical components, circuits, semiconductor devices, etc., can solve problems such as low yield, achieve the effects of reducing contact area, ensuring gate line width, and suppressing parasitic capacitance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

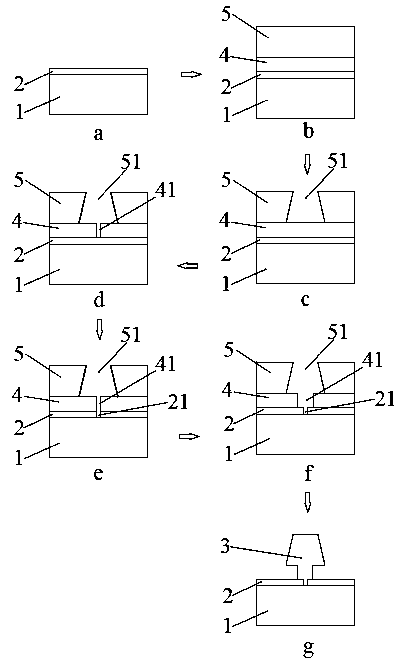

[0055] Embodiment 1: In this embodiment, the substrate 1 is preferably a gallium nitride (GaN) epitaxial wafer. refer to figure 2 The production method flowchart of middle a-f comprises the following steps: as figure 2 As shown in a, 1) GaN substrate 1 is cleaned, and silicon nitride is deposited on the GaN epitaxial wafer. In this embodiment, the thickness of deposited silicon nitride is 50nm.

[0056] Such as figure 2As shown in b, 2) Spin-coat PMMA electron beam photoresist 4 with a thickness of 350 nm on silicon nitride and bake it on a hot plate at 180°C for 2 minutes. After cooling to room temperature, continue to spin-coat Nloff5510 I-Line with a thickness of 800 nm Negative photoresist 5 was baked on a hot plate at 100°C for 2 minutes.

[0057] Such as figure 2 As shown in c, 3) Nloff5510 I-Line negative photoresist 5 exposure, the preferred energy is 1300J / m 2 , developed with 2.38% TMAH (tetramethylammonium hydroxide) at 23°C for 41 seconds. Oxygen plasma t...

Embodiment 2

[0064] Embodiment 2: In this embodiment, the substrate 1 is preferably a gallium arsenide (GaAs) epitaxial wafer. refer to figure 2 The production method flowchart of middle a-f comprises the following steps: as figure 2 As shown in a, 1) GaAs epitaxial wafer is cleaned, and silicon nitride is deposited on the GaAs epitaxial wafer. In this embodiment, the thickness of deposited silicon nitride is 50nm.

[0065] Such as figure 2 As shown in b, 2) Spin-coat PMMA electron beam photoresist 4 with a thickness of 100 nm on silicon nitride and bake it on a hot plate at 180°C for 2 minutes. After cooling to room temperature, continue to spin-coat Nloff5510 I-Line with a thickness of 600 nm Negative photoresist 5 was baked on a hot plate at 100°C for 2 minutes.

[0066] Such as figure 2 As shown in c, 3) Nloff5510 I-Line negative photoresist 5 exposure, the preferred energy is 1300J / m 2 , developed with 2.38% TMAH (tetramethylammonium hydroxide) at 23°C for 41 seconds. Oxygen...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com