Semiconductor contact structure, memory structure and preparation method

A memory and semiconductor technology, applied in the fields of semiconductor/solid-state device manufacturing, semiconductor devices, electric solid-state devices, etc., can solve the problems affecting the structural performance of the memory, the consumption of the connection pad layer, and the small width of the connection part of the memory cell node.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

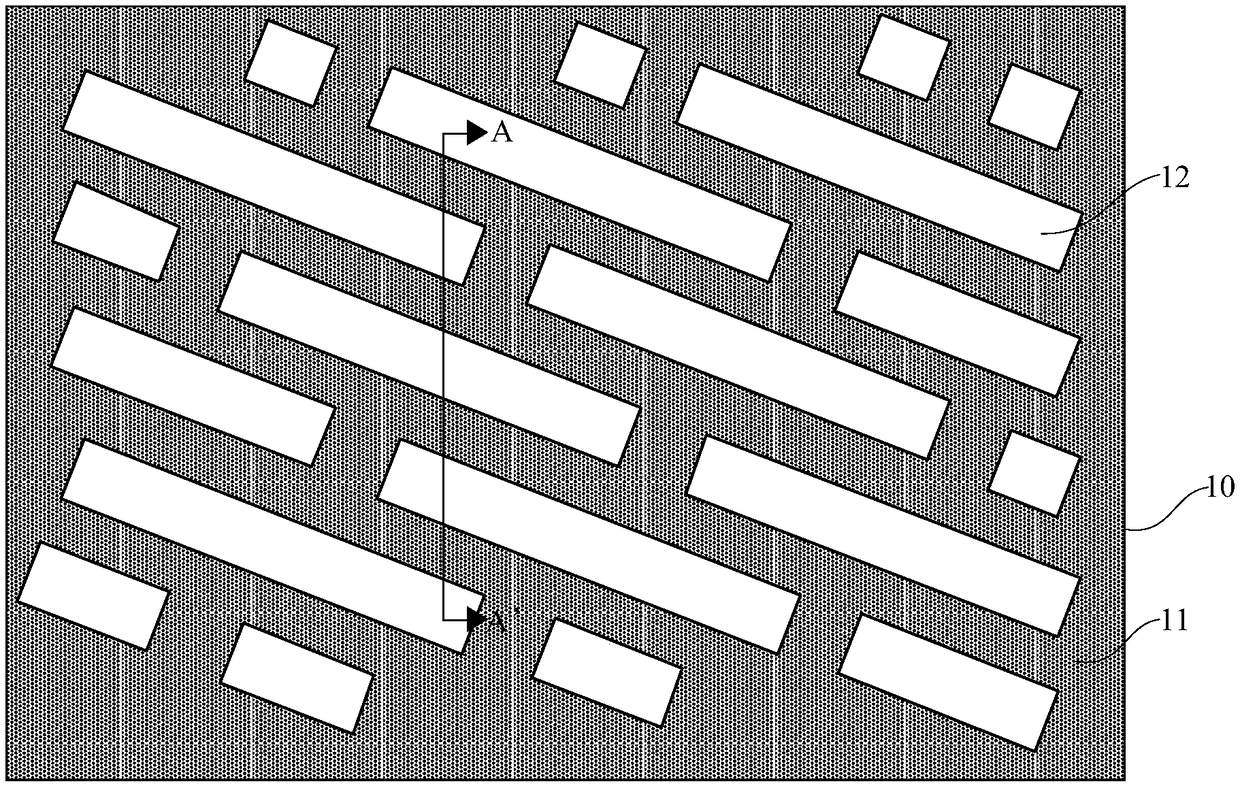

[0158] like figure 1 As shown, the present invention provides a method for preparing a memory structure, and the method for preparing the memory structure includes the following steps:

[0159] 1) A semiconductor substrate is provided, and several shallow trench isolation structures are formed in the semiconductor substrate, and the shallow trench isolation structures isolate several active regions arranged at intervals in the semiconductor substrate;

[0160] 2) Embedding several word lines arranged in parallel at intervals in the semiconductor substrate, the extending direction of the word lines intersects with the extending direction of the length of the active region at a first angle less than 90 degrees;

[0161] 3) forming a plurality of bit lines arranged in parallel at intervals on the semiconductor substrate, the extension direction of the bit lines intersects with the extension direction of the active region at a second angle less than 90 degrees, and the bit lines ...

Embodiment 2

[0219] Please combine Figure 1 to Figure 20 read on Figure 22 , the present invention also provides a memory structure, the memory structure includes: a semiconductor substrate 10, the semiconductor substrate 10 is formed with several shallow trench isolation structures 11, and the shallow trench isolation structures 11 isolate several Active regions 12 arranged at intervals in the semiconductor substrate 10; several word lines 13 arranged in parallel at intervals, the word lines 13 are buried in the semiconductor substrate 10, and the extension of the word lines 13 The direction intersects the lengthwise extending direction of the active region 12 at a first angle α less than 90 degrees; several bit lines 14 arranged in parallel at intervals, the bit lines 14 are located on the semiconductor substrate 10, the The extending direction of the bit line 14 intersects with the extending direction of the active region 12 at a second angle β less than 90 degrees, and the extending...

Embodiment 3

[0238] see Figure 23 , the present invention also provides a method for preparing a semiconductor contact structure, the method for preparing a semiconductor contact structure includes the following steps:

[0239] 1) providing a semiconductor substrate, in which functional devices are formed;

[0240] 2) forming a contact hole in the semiconductor substrate, the contact hole exposing the functional device;

[0241] 3) forming a conductive material layer in the contact hole and on the surface of the semiconductor substrate;

[0242] 4) using an etch-back process to etch and remove the conductive material layer located on the surface of the semiconductor substrate to form a conductive layer located in the contact hole, the conductive layer is electrically connected to the functional device; the conductive plug The upper surface of is not higher than the upper surface of the semiconductor substrate;

[0243] 5) forming a reconfiguration mask layer on the upper surface of the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com