Semiconductor structure forming method

A semiconductor and gate structure technology, applied in the field of semiconductor structure formation, can solve the problem that the electrical performance of the semiconductor structure needs to be improved, etc., to improve the dielectric relaxation problem, the positive bias voltage-temperature instability characteristic and the negative bias voltage- The effect of improving temperature instability characteristics and reducing the content of oxygen vacancies

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

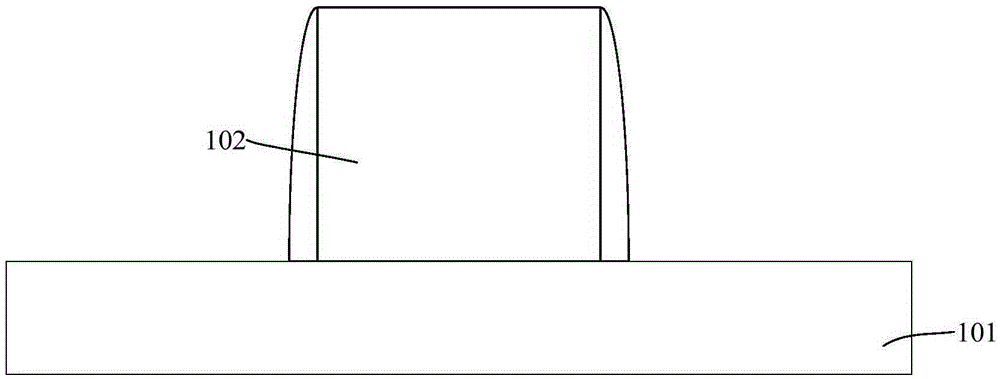

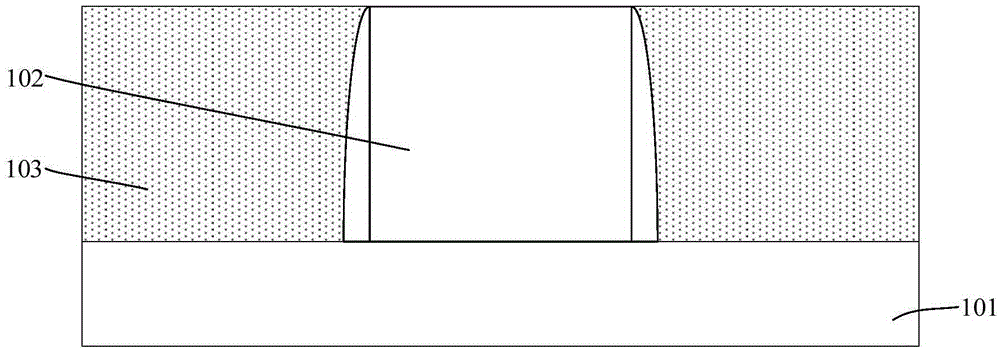

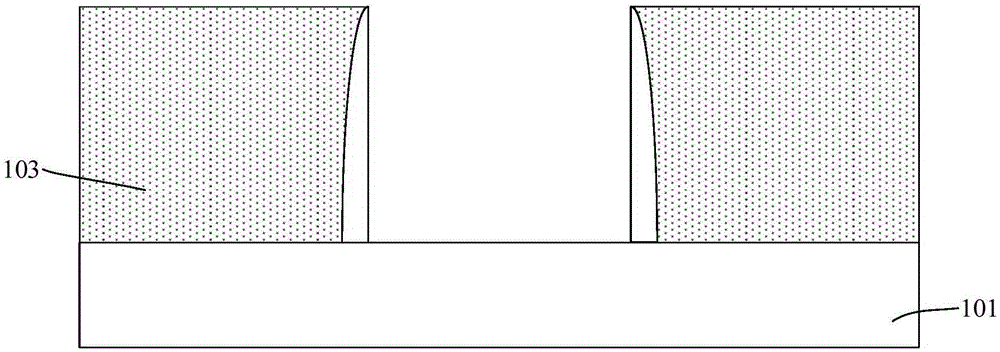

[0032] As mentioned in the background art, the electrical performance of the semiconductor structure formed in the prior art needs to be improved.

[0033] It has been found through research that although the use of a high-k gate dielectric material as the material of the gate dielectric layer can improve the electrical performance of the semiconductor structure to a certain extent, for example, the leakage current (leakagecurrent) in the semiconductor structure is reduced, however, the semiconductor structure The relaxation current (DR Current, DielectricRelaxation Current) is still large, resulting in poor electrical performance of the semiconductor structure, for example, the positive bias-temperature instability characteristics (PBTI, Positive Biase Temperature Instability) and negative bias-temperature instability of the semiconductor structure The stability characteristic (NBTI, Negative Biase Temperature Instability) is remarkable. Further studies have found that the re...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com