Tunneling field effect transistor inhibiting output non-linear opening and preparing method of tunneling field effect transistor

A tunneling field effect and transistor technology, which is applied in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the problems of low on-state current, failure to meet system integration application requirements, and low band tunneling efficiency. Achieving a steep sub-threshold slope, improving the output characteristics of the device, and suppressing the nonlinear turn-on phenomenon

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

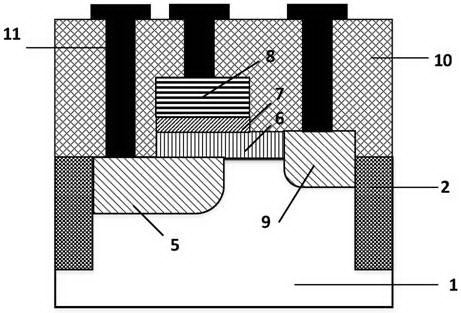

[0043] The implementation method of the tunneling field effect transistor for suppressing output nonlinear turn-on according to the present invention will be further described through specific embodiments below in conjunction with the accompanying drawings.

[0044] The specific implementation steps are as Figure 1-Figure 7 Shown: (This example takes N-type devices as an example, and P-type devices can be deduced by analogy)

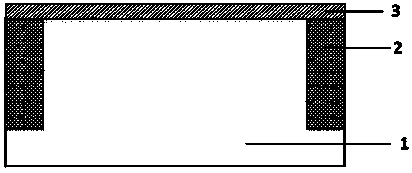

[0045] 1. The substrate doping concentration is lightly doped (about 1E13cm -3 -1E15cm -3 ), a layer of silicon dioxide 3 is initially thermally oxidized on a Si substrate 1 with a crystal orientation of , with a thickness of about 10 nm, and a layer of silicon nitride (Si 3 N 4 ), with a thickness of about 100nm, and then use shallow trench isolation technology to make STI isolation 2 in the active area, and then perform CMP, such as figure 2 shown;

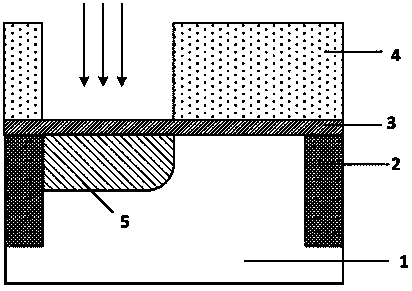

[0046] 2. Expose the tunneling source region 5 by photolithography, and use the photoresist 4 as...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com