Vertical channel dual-mechanism conduction nanowire tunneling transistor and preparation method

A vertical channel, dual-mechanism technology, applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the problems that cannot meet the requirements of system integration applications, low on-state current, and low efficiency of band-band tunneling. Achieve the effects of suppressing leakage current and bipolar effect, steep sub-threshold slope, and high performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

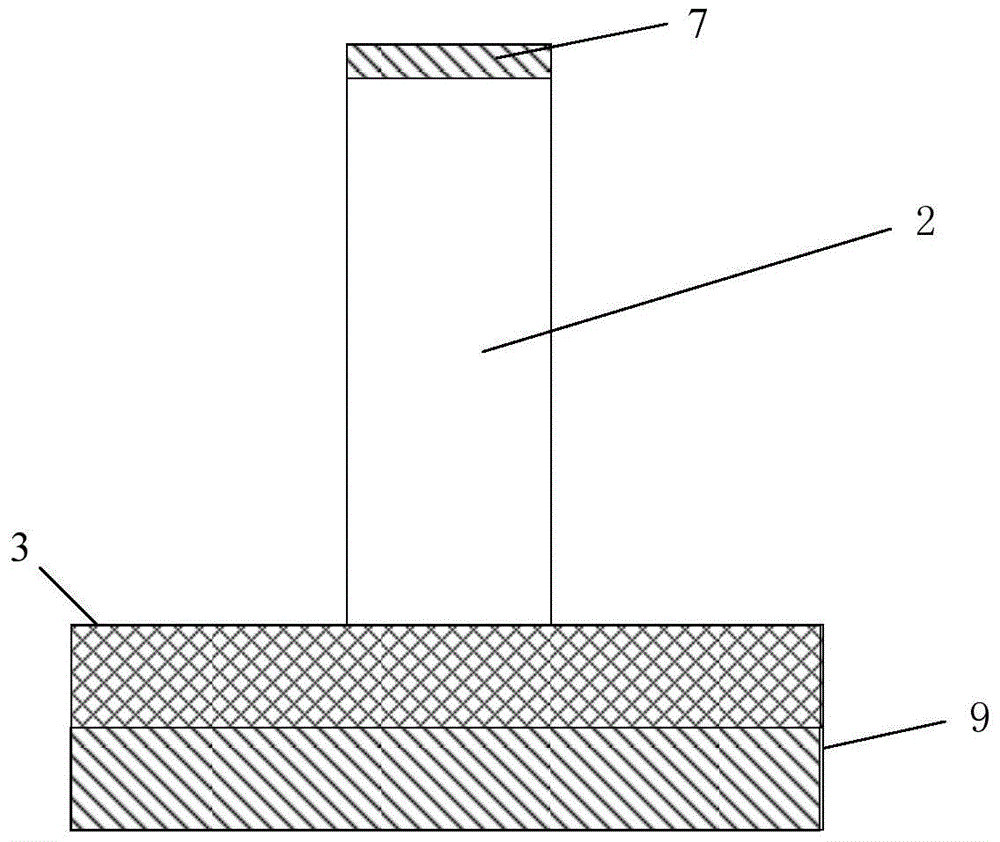

[0046] The implementation method of the vertical structure bipolar mixed conduction double gate tunneling transistor described in the present invention will be further described through specific embodiments below in conjunction with the accompanying drawings

[0047] The specific implementation steps are as Figure 2-Figure 6 Shown: (taking N-type devices as an example)

[0048] 1. Ion implantation to the thermionic emission source region (As, 1E15 / cm -2 , 20keV);

[0049] 2. Epitaxial growth tunneling source region, ion implantation (BF 2 , 1E15 / cm -2 , 20keV);

[0050] 3. Epitaxially lightly doped or undoped Si at the tunnel source region, and deposit a layer of Si on it 3 N 4 Film, photolithography, using RIE to deeply etch the vertical channel region, the width of the channel region is 5nm-100nm, such as figure 2 ;

[0051] 4. Form a gate oxide layer (5nm) by thermal oxidation, and then use LPCVD to deposit polysilicon gates of nanowires such as image 3 shown. ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com