Method for achieving silicon through hole laminated chip interconnection

A through-silicon via and chip technology, applied in semiconductor devices, electrical components, circuits, etc., can solve problems such as low reliability of solder joints, long bonding time, and affecting joint performance, and achieve excellent comprehensive mechanical properties and shorten bonding time. The effect of time, excellent bonding effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach 1

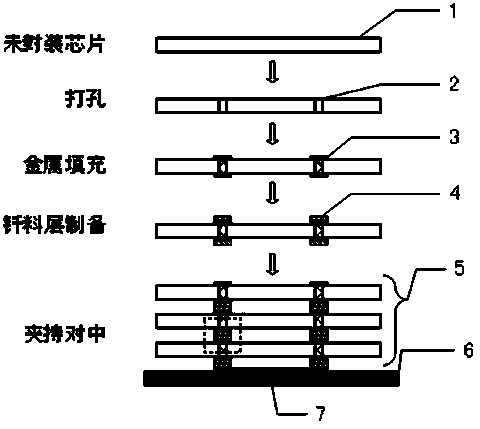

[0026] Specific implementation mode one: as Figure 1~5 As shown, this embodiment provides a method for realizing TSV all-intermetallic solder joint bonding by current Joule heat. In this embodiment, strong current bonding of multi-layer stacked TSV chips is carried out according to the following steps:

[0027] (1) Drilling: Drilling the chip 1, the specific method is: forming a through hole 2 in the silicon crystal by etching or laser drilling, and then using plasma enhanced chemical vapor deposition (PECVD), physical vapor deposition (PVD) ) or Metal Organic Compound Chemical Vapor Deposition (MOCVD) to sequentially deposit metal adhesion layer Ti or Ta, barrier layer TiN or TaN / A seed layer (Cu, Ag or Ag) to obtain a through-silicon via chip packaged on a stack, and the thickness of the chip is less than 100 μm;

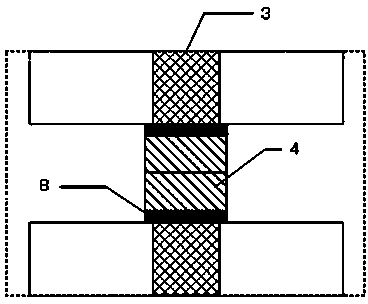

[0028] (2) Filling of conductive metal and flattening of pads: use electroplating to fill the through-hole 2 conductive metal 3 of the laminated package thr...

Embodiment approach 2

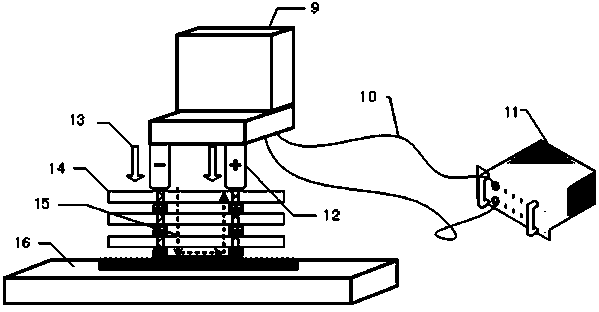

[0033] Specific implementation method two: such as Image 6 As shown, this embodiment provides a method for realizing all-intermetallic compound solder joint bonding in a current-ultrasonic composite field, and the steps are as follows:

[0034] (1)~(4) Repeat steps (1)~(4) in the specific implementation method 1;

[0035] (5) An ultrasonic device is integrated in the processing platform 16 so that the ultrasonic contact 19 is flush with the surface of the processing platform 16 . First turn on the double-pulse narrow-gap parallel resistance welding equipment 9 to start the DC power switch 11, and when the electrode contacts 12 press the stacked chips 5 under pneumatic action, the ultrasonic power supply 20 is quickly turned on. The current intensity is appropriately reduced to the range of 0.6~1.0KA, the pressure 13 of the electrode contact 12 needs to be appropriately increased (3~10N), the chip is placed and moved, the bonding time is 90ms~1000ms, the ultrasonic frequency ...

Embodiment approach 3

[0037] Specific implementation method three: such as Figure 7As shown, this embodiment provides a low temperature current Joule heating to realize TSV all-intermetallic compound solder joint bonding, and the steps are as follows:

[0038] (1)~(4) Repeat steps (1)~(4) in the specific implementation method 1;

[0039] (5) Place the heating plate device 21 on the processing platform 16 . Turn on the power supply 22 of the heating plate 30s in advance to preheat the device to be processed, and the preheating temperature is 50-150°C. Then turn on the double-pulse narrow-gap parallel resistance welding equipment 9, start the DC power switch 11, and the electrode contact 12 will press the stacked chip 5 under pneumatic action, and form a closed circuit in the solder joint 18-pad 8-substrate copper wiring 7 The current of the loop is 15; the control current intensity is 0.6KA~1.2KA, the welding time is 90ms~1500ms, and the pressure 13 of the electrode contact is 2~8N. The process ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| electrical conductivity | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com