Manufacturing method of precisely-aligned bridged-grain polysilicon thin film transistor

A technology of polysilicon thin film and manufacturing method, which is applied in the direction of transistor, semiconductor/solid-state device manufacturing, semiconductor device, etc., to achieve the effects of precise alignment, simplified process, and uniform electrical characteristics

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0035] This embodiment provides a method for manufacturing a bridged grain polysilicon thin film transistor, such as Figure 4a-4c Shown, including:

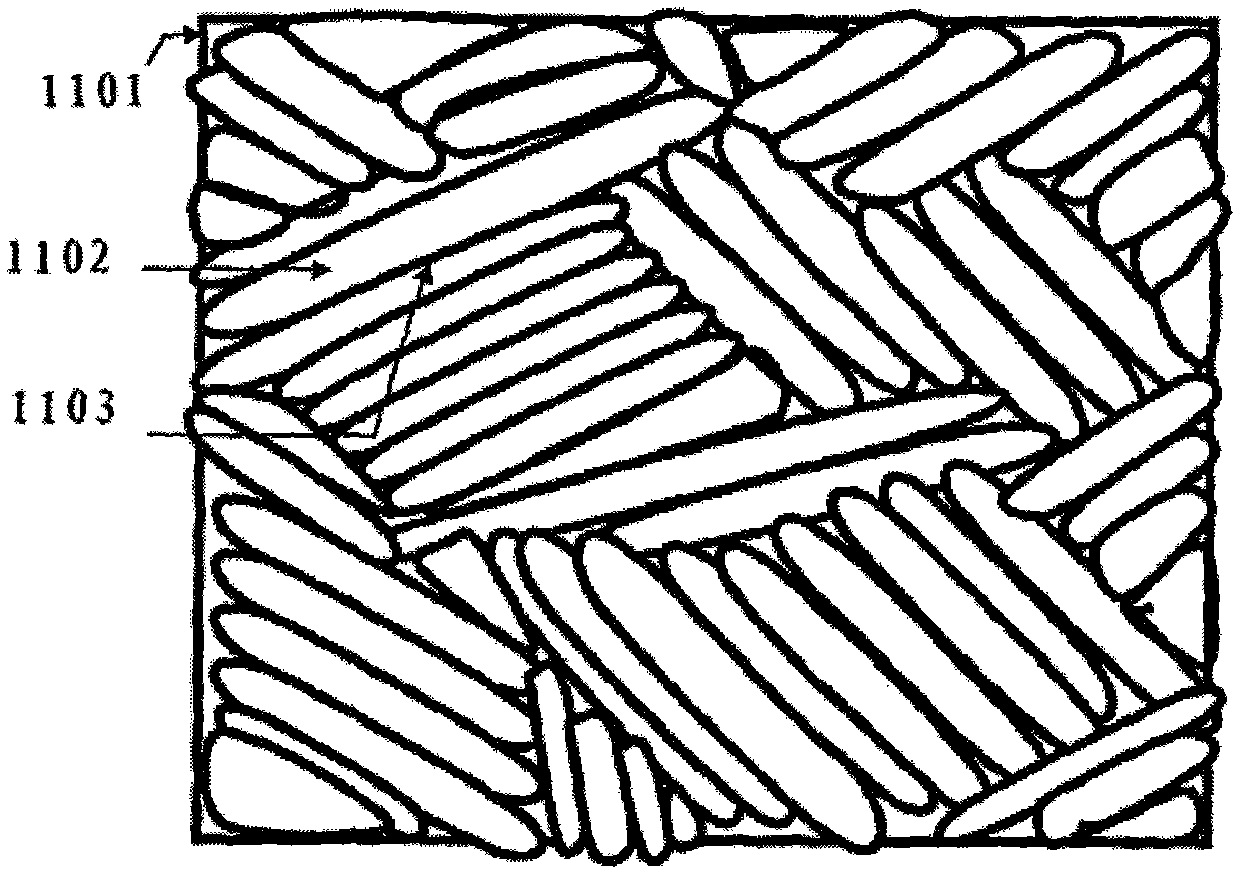

[0036] 1) Deposit a layer of low temperature oxide (LTO) on the glass substrate 101 as the barrier layer 102, and form a polysilicon layer 103 on the barrier layer 102;

[0037] 2) Etching the polysilicon layer 103 into isolated silicon islands;

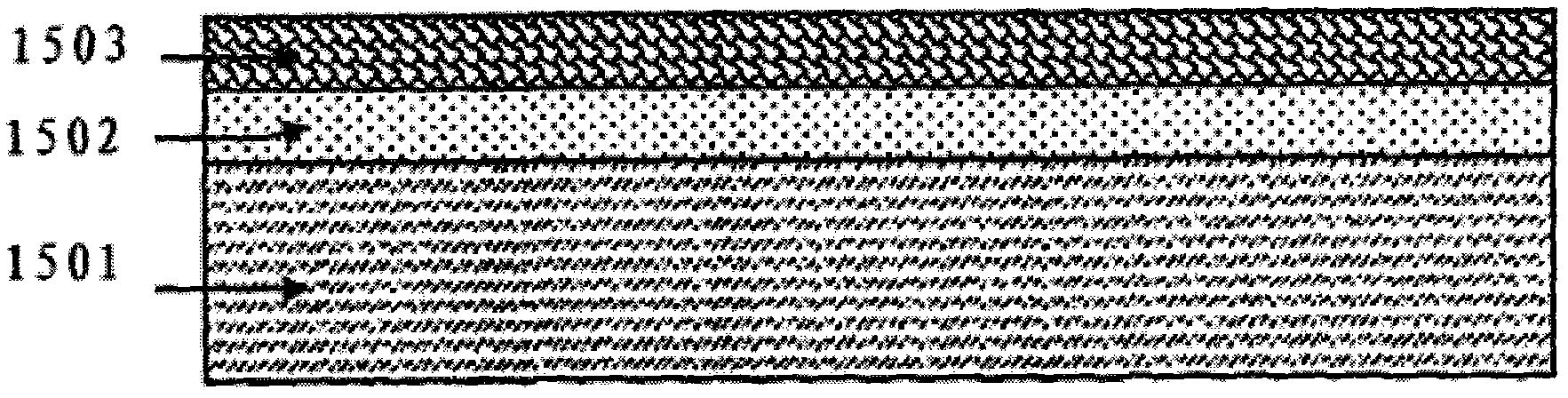

[0038] 3) Using LPCVD (low pressure chemical vapor deposition) method to directly deposit the LTO gate insulating layer 201 on the polysilicon layer 103;

[0039] 4) Depositing 200 nm of low-temperature polysilicon on the gate insulating layer 201 as the gate layer 301;

[0040] 5) Coating a 1 micron positive photoresist 401 for etching on the gate layer 301;

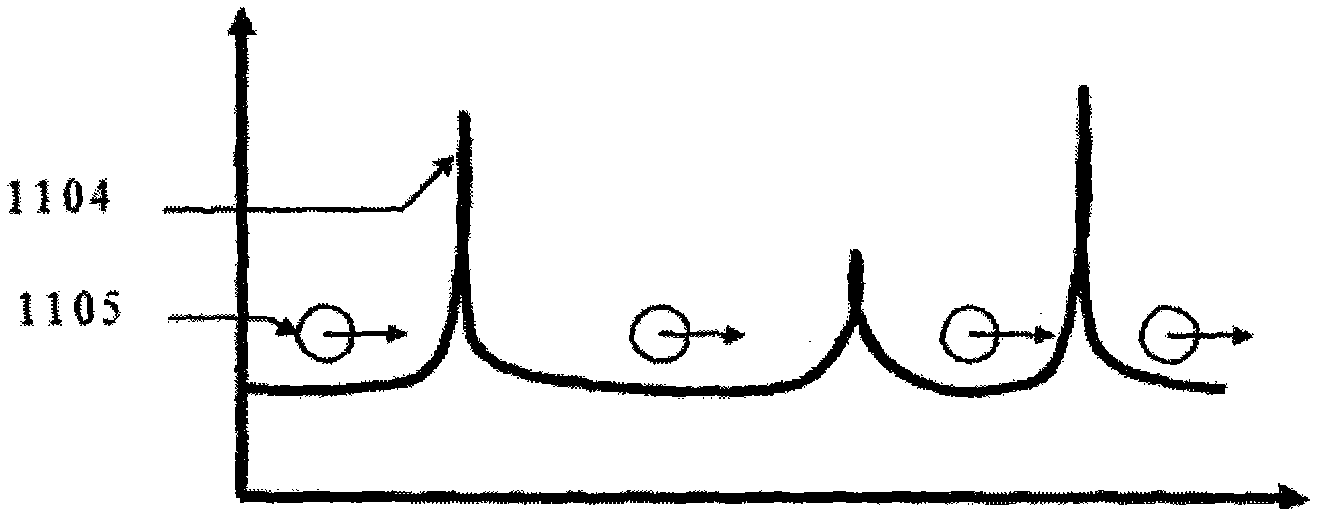

[0041] 6), such as Figure 4a As shown, a grayscale photolithography mask is used for exposure. The grayscale photolithography mask includes light-transmitting areas 701 on both sides, and alternately arranged opaque areas 702 and partiall...

Embodiment 2

[0048] This embodiment provides a method for manufacturing a bridged grain polysilicon thin film transistor, such as Figure 4a , 4b , 5a, 5b, including:

[0049] 1), such as Figure 4a As shown, a layer of low temperature oxide (LTO) is deposited on the glass substrate 101 as the barrier layer 102, and a polysilicon layer 103 is formed on the barrier layer 102;

[0050] 2) Etching the polysilicon layer 103 into isolated silicon islands;

[0051] 3) Using LPCVD (low pressure chemical vapor deposition) method to directly deposit the LTO gate insulating layer 201 on the polysilicon layer 103;

[0052] 4) Depositing 200 nm of low-temperature polysilicon on the gate insulating layer 201 as the gate layer 301;

[0053] 5) Coating a 1 micron positive photoresist 401 for etching on the gate layer 301;

[0054] 6), such as Figure 4a As shown, a grayscale photolithography mask is used for exposure. The grayscale photolithography mask includes light-transmitting areas 701 on both sides and altern...

Embodiment 3

[0062] This embodiment provides a method for manufacturing a bridged grain polysilicon thin film transistor, such as Figure 6a-6c Shown, including:

[0063] 1) Deposit a layer of low temperature oxide (LTO) on the glass substrate 101 as the barrier layer 102, and form a polysilicon layer 103 on the barrier layer 102;

[0064] 2) Etching the polysilicon layer 103 into isolated silicon islands;

[0065] 3) Using LPCVD (low pressure chemical vapor deposition) method to directly deposit the LTO gate insulating layer 201 on the polysilicon layer 103;

[0066] 4) Depositing 200 nm of low-temperature polysilicon on the gate insulating layer 201 as the gate layer 301;

[0067] 5) Coating a 1 micron positive photoresist 401 for etching on the gate layer 301;

[0068] 6), such as Figure 6a As shown, a photolithography mask is used for exposure. The photolithography mask includes fully transparent regions 701 on both sides and alternately arranged non-transmissive regions 702 and fully transparen...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com