Manufacturing method of germanium-silicon heterojunction bipolar triode device

A technology of heterojunction bipolar, manufacturing method, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as process instability, increased defects, base-collector junction leakage, etc., and achieve stability Process flow, process cost reduction, and the effect of high product yield

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

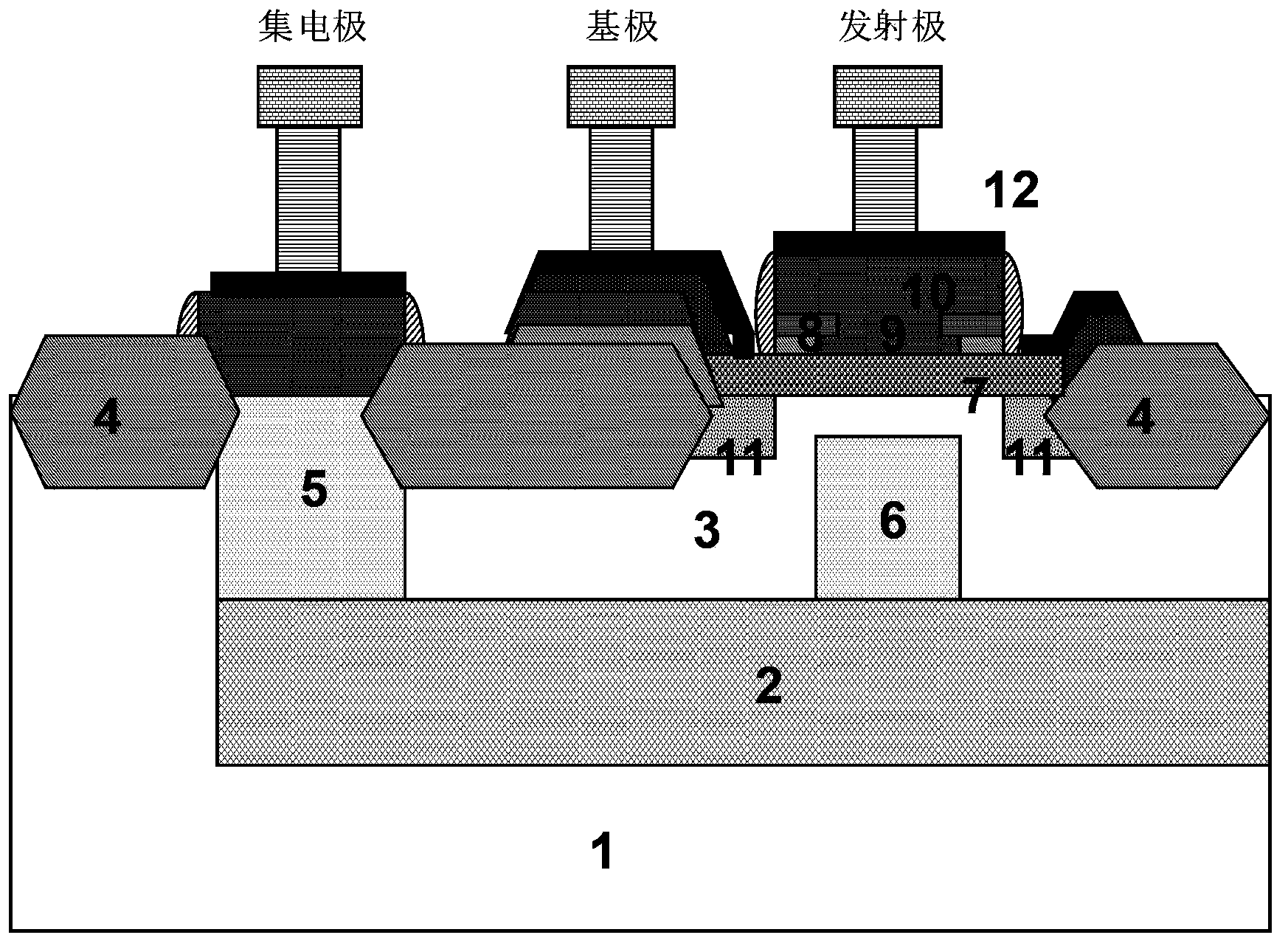

[0026] The present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

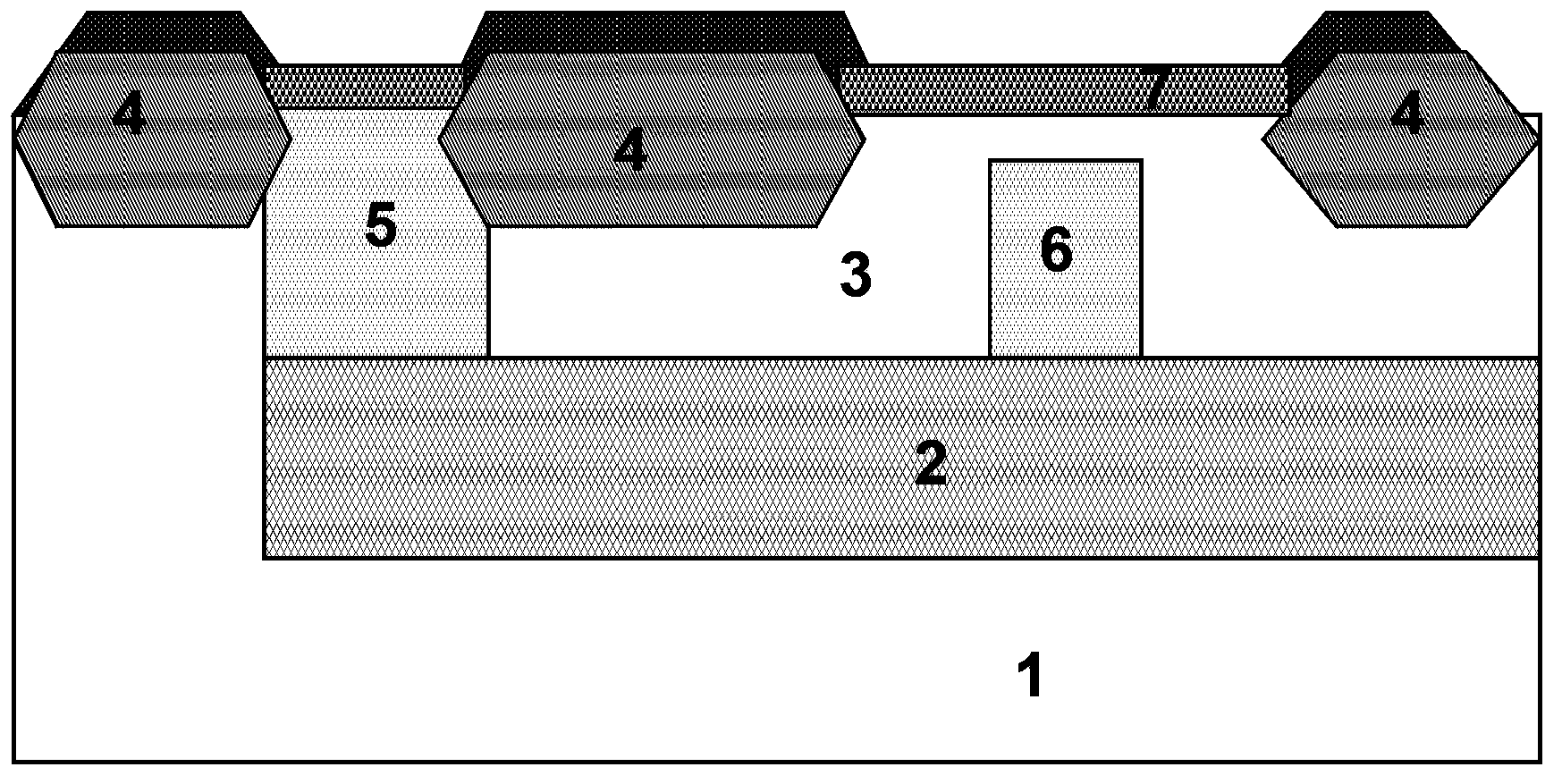

[0027] The manufacturing method of silicon germanium heterojunction bipolar transistor device of the present invention, as Figure 11 shown, including the following steps:

[0028] Step 1, forming an N-type buried layer 2 on the P-type silicon substrate 1, the N-type buried layer 2 is heavily doped, the implanted ions are impurity arsenic that diffuses less upwardly when the thermal overhead is high, and the implantation energy is 30 ~120keV, the dose is 10 15 ~10 16 cm -2 Carry out high-temperature propulsion using a furnace tube, the propulsion temperature is 1000-1100°C, and the time is 30-120 minutes, and then low N-doped epitaxy 3 growth is performed on the N-type buried layer 2, and the doped impurity is phosphorus. The impurity concentration is 2×10 15 ~5×10 16 cm -3 ; Perform N-type ion implantation on the N-type buried...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com