Metal gate field effect transistor and method of making the same

A technology for field effect transistors and manufacturing methods, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of increasing aspect ratio and increasing difficulty of filling metal, so as to reduce parasitic resistance and save Process cost, effect of saving process steps

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

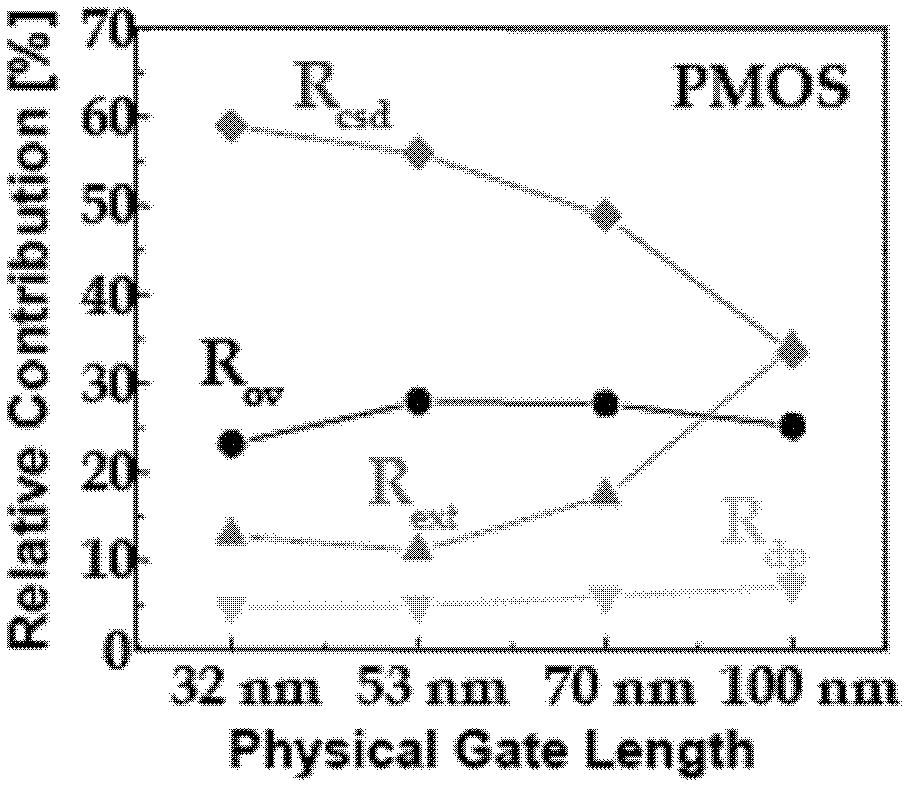

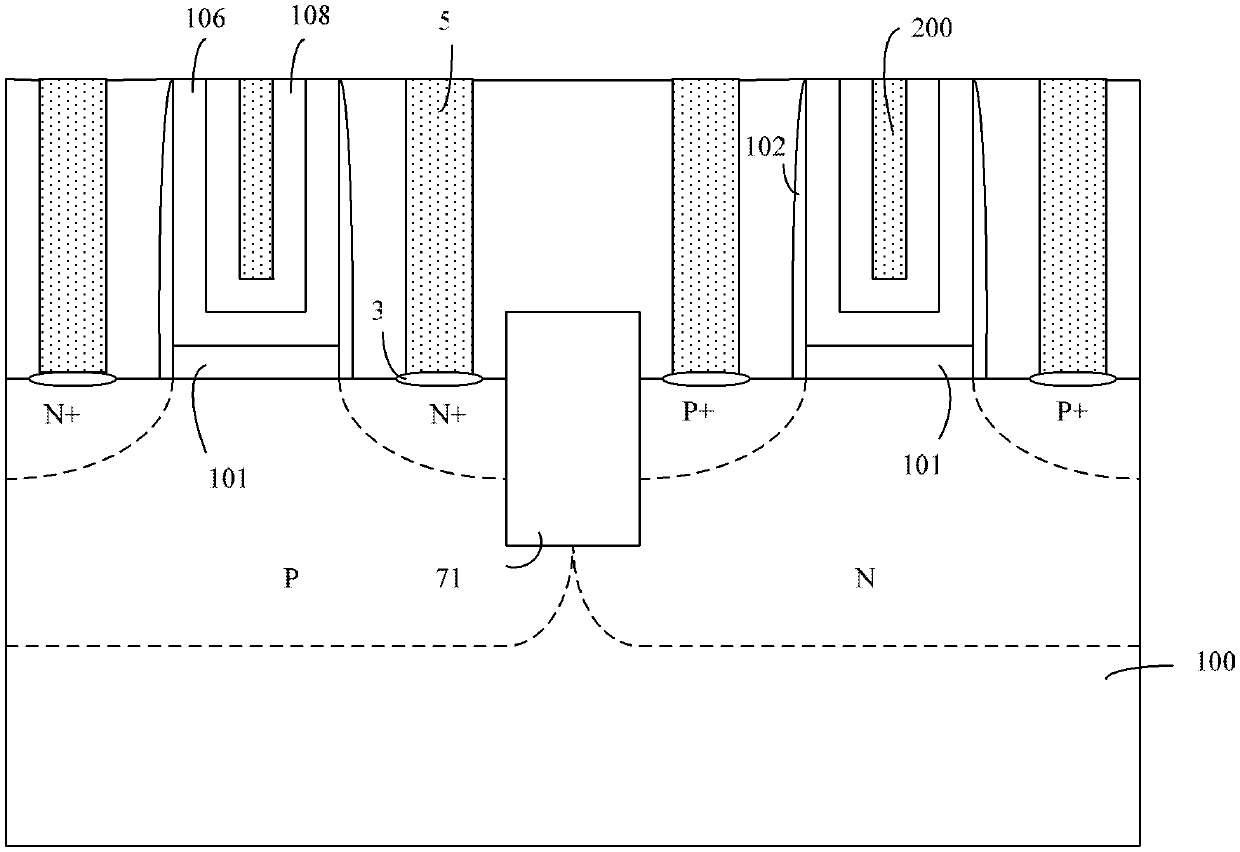

[0027] The present invention provides a method for manufacturing a metal gate field effect transistor, which uses a gate-last process to fabricate a dummy gate, and then forms at least a part of the metal gate stack and the source and drain by electroless plating (Electroless deposition, electroless plating) contact holes. In the present invention, the last layer of the metal gate and the contact holes of the source and drain electrodes are formed by means of electroless metal plating, so that the trenches and contact holes formed by the metal in the metal gate are used in through holes with high aspect ratios. The metal texture is dense and uniform, and there are no voids and cracks; and the present invention forms the last layer of metal of the metal gate together with the contact hole, which saves process steps, improves process efficiency and saves process cost; at the same time, the present invention The parasitic resistance Rcsd of the contact hole and the drain is reduc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com