Fan-out Panel Level ball grid array (BGA) package part manufacture process

A manufacturing process and packaging technology, which is used in semiconductor/solid-state device manufacturing, electrical components, electrical solid-state devices, etc. The number of pins, better performance requirements, and high packaging costs can shorten the current and signal transmission distance, reduce warpage, improve electrical performance and product reliability.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

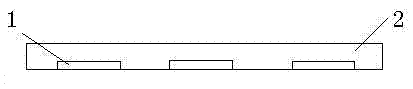

[0021] The present invention will be described in further detail below in conjunction with the accompanying drawings.

[0022] As shown in the figure: A manufacturing process of Fan-out Panel Level BGA package, which is carried out according to the following steps:

[0023] The first step, wafer thinning: use the anti-fragmentation process to thin the wafer to the specified thickness;

[0024] The second step, wafer dicing: the wafer with a thickness of 150 μm or more adopts the ordinary dicing process, and the wafer with a thickness of less than 150 μm adopts a double-knife dicing machine and its process;

[0025] The third step, flipping the core: before flipping the core, adhere the double-sided adhesive film 7 to the high temperature resistant glass 11 with a smooth and flat surface, wherein the thickness of the double-sided adhesive film 7 should not be large. It must be less than 3um, and the front of the film needs to mark the position of the core in advance, set up an...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com