Insulated gate bipolar transistor (IGBT) with deep energy level impurity implantation

A technology of bipolar transistors and deep-level impurities, which is applied to semiconductor devices, electrical components, circuits, etc., can solve the problems of device avalanche breakdown, small conduction voltage drop, and increased leakage current, and achieve accelerated recombination, reduced Small high temperature leakage current, the effect of reducing the overall power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

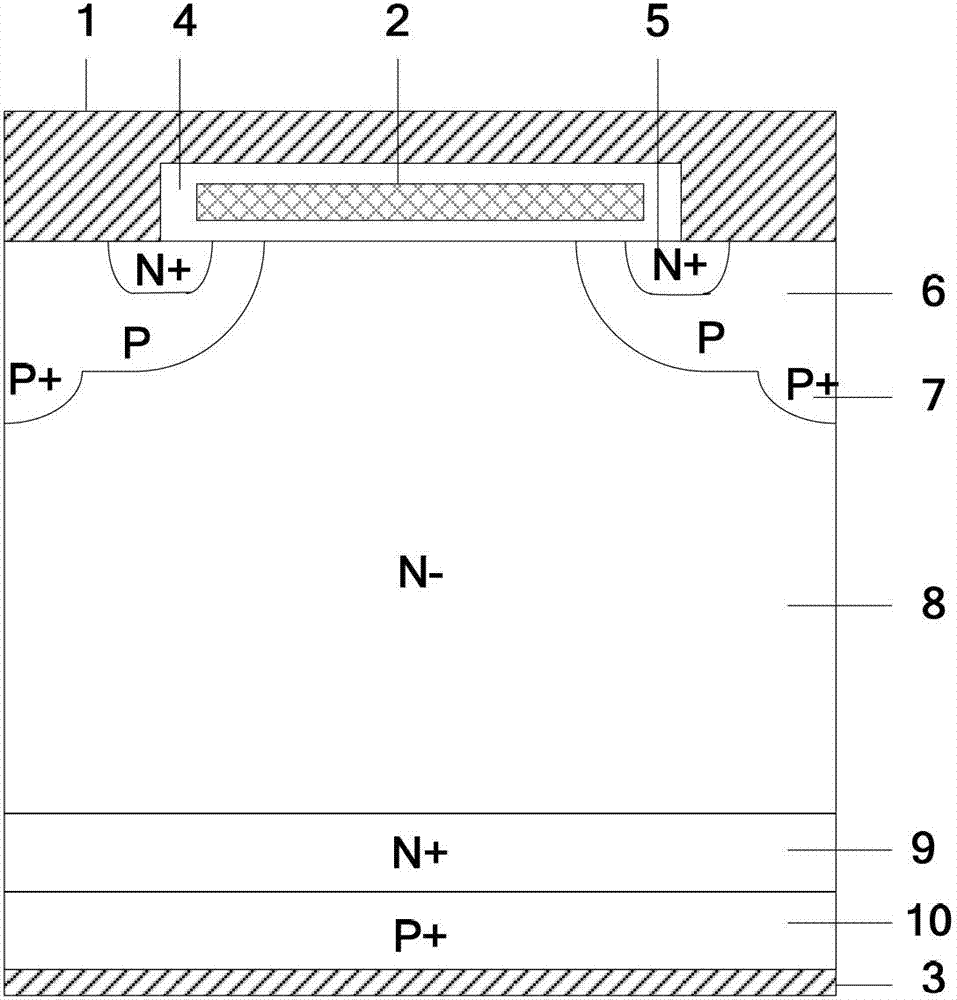

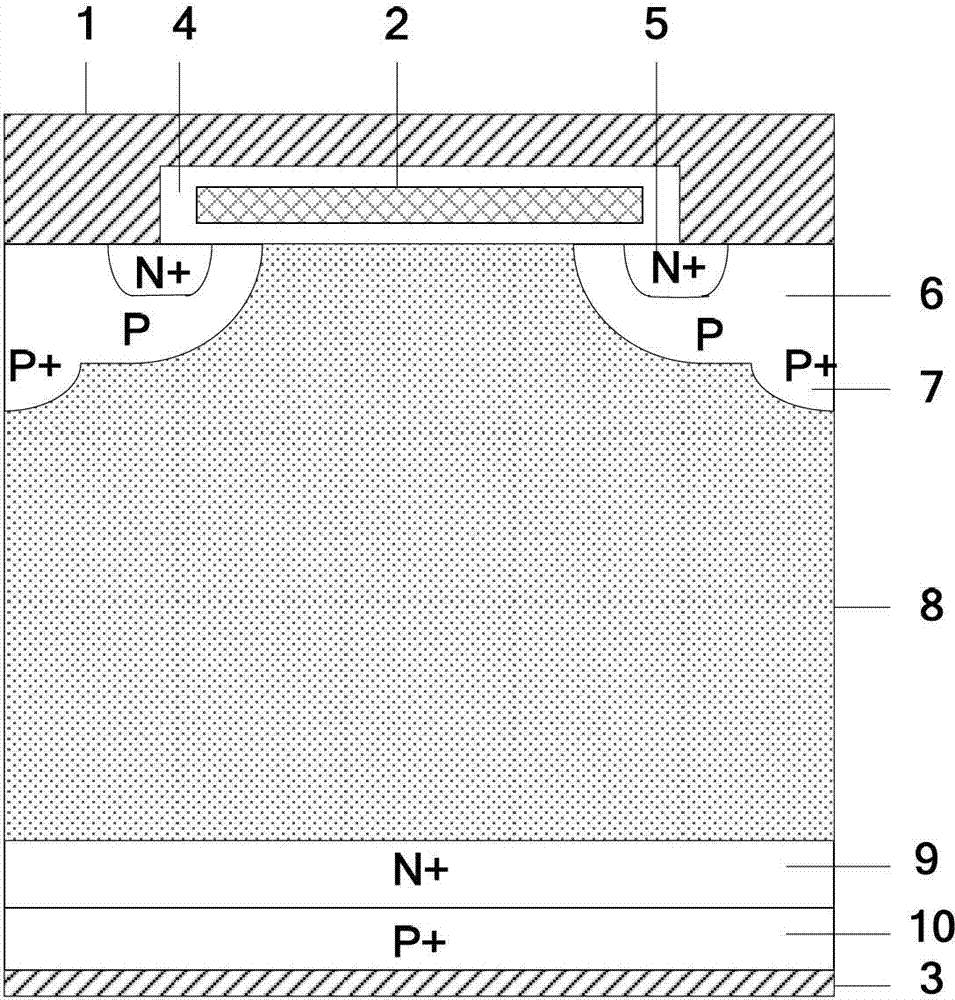

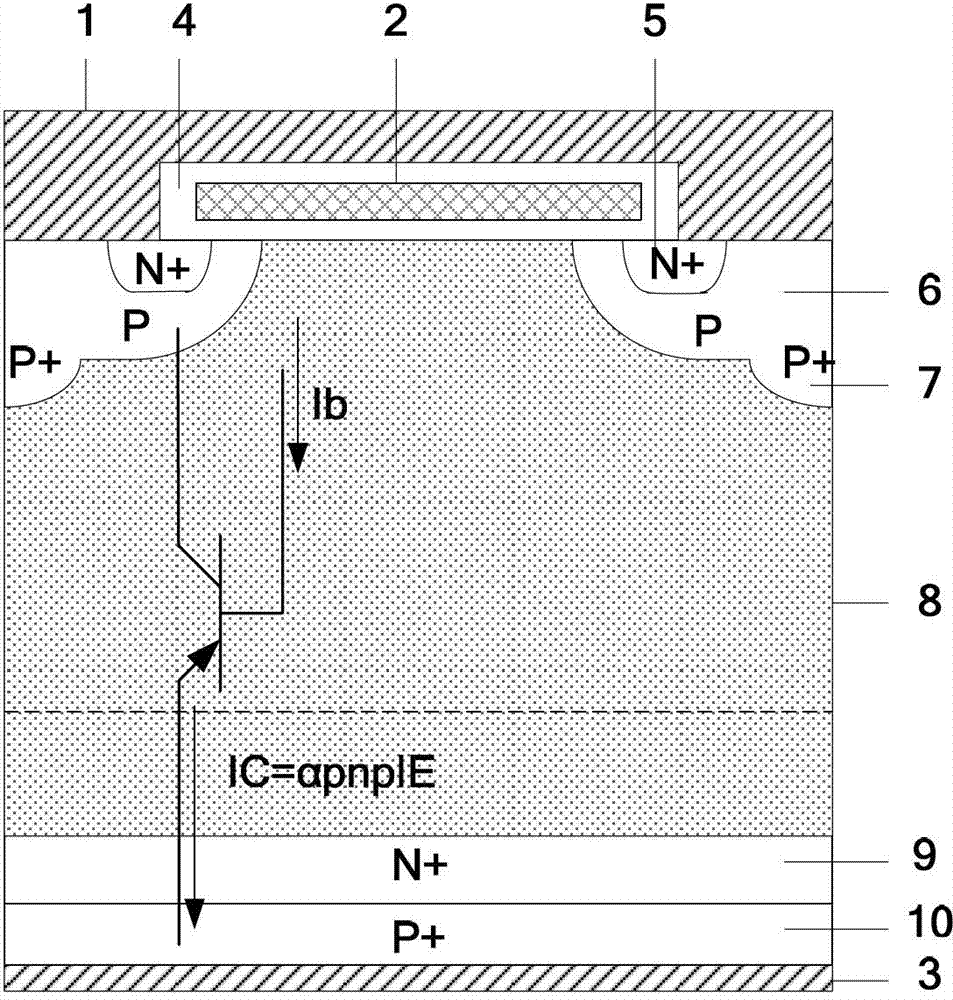

[0018] An insulated gate bipolar transistor with deep level impurity implantation, its cell structure is as follows figure 2 As shown, including active emitter 1, polysilicon gate electrode 2, metal collector 3, silicon dioxide gate oxide layer 4, N+ active region 5, P-type base region 6, P+ body region 7, N-drift region 8 , N+ field stop layer 9, P+ collector region 10; the device is metallized collector 3, P+ collector region 10, N+ field stop layer 9, N-drift region 8, and P-type base region 6 is located in On both sides of the top of the N-drift region 8, there is an N+ active region 5 in the P-type base region 6, and the P+ body region 7 is located on both sides of the N-drift region 8 below the P-type base region 6, and is connected to the P-type base region 6 and The N-drift regions 8 are in contact with each other; the active emitter 1 is in contact with the N+ active region 5 and the P-type base region 6 on both sides of the cell surface, and the active emitter 1 is i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com