Advanced four-side flat pin-free package and manufacturing method thereof

A leadless packaging, four-sided flat technology, applied in semiconductor/solid-state device manufacturing, electrical components, electric solid-state devices, etc., can solve problems such as limiting the number of I/O, shortening the life of cutting blades, pin failure, etc., to prevent The failure of pin welding, the improvement of surface mount quality, and the effect of preventing chip drift

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0071] The present invention is described in detail below in conjunction with accompanying drawing:

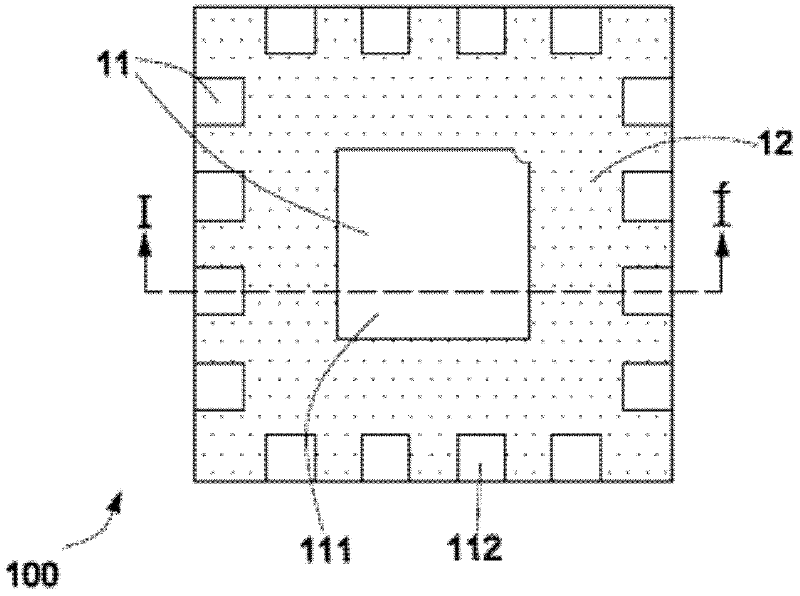

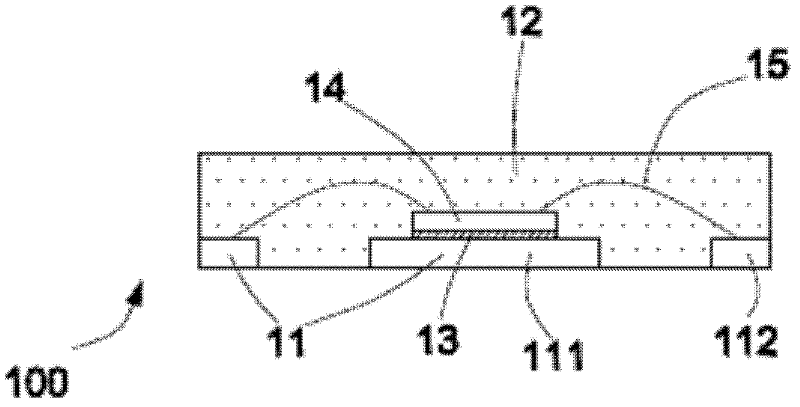

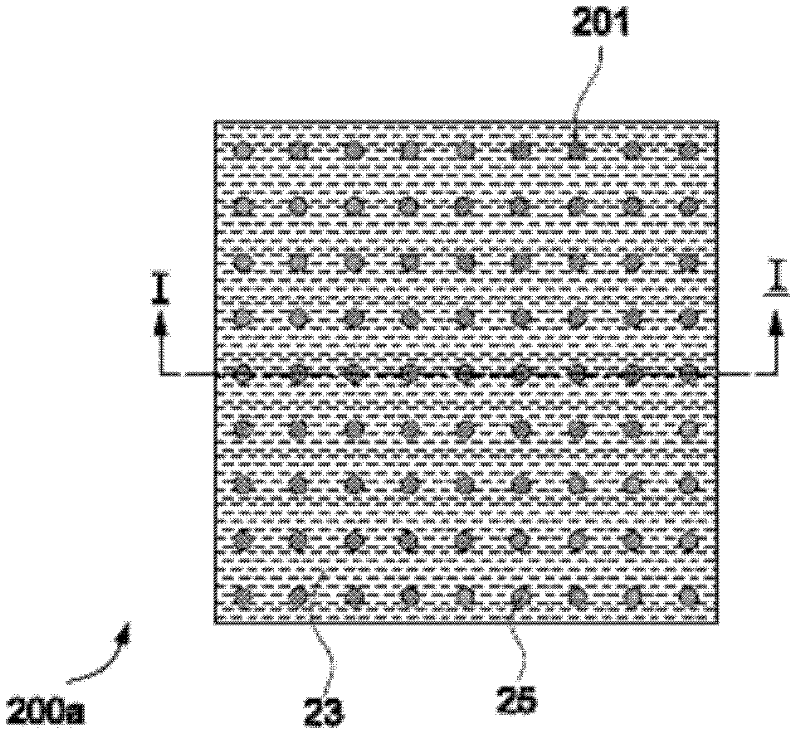

[0072] Figure 2A A schematic diagram of the rear side of an advanced QFN package structure in which the cross-section of the pins is circular and the pins are arranged in parallel in an area array pin arrangement according to an embodiment of the present invention. Figure 2B A schematic diagram of the rear side of an advanced QFN package structure in which the cross-section of the pins is rectangular and the pins are arranged in parallel in an area array pin arrangement according to an embodiment of the present invention.

[0073] Refer to the above Figure 2A -B It can be seen that, in this embodiment, the advanced QFN package structures 200a and 200b arranged in an area array have pins 201 arranged in an area array, and the arrangement of the pins 201 is parallel. A metal material layer 25 is disposed on the lower surface of the pins 201 , and an insulating filling mater...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com