Matrix dual in-line package (DIP) lead frame, integrated circuit (IC) packages based on frame and production method of IC packages

A lead frame and matrix technology, which is applied in the field of IC chip packages, can solve the problems of high safety risk of DIP manual processing molds, high error rate in the processing process, and low material utilization rate, so as to optimize the production configuration scheme and improve the utilization rate. , the effect of improving utilization

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

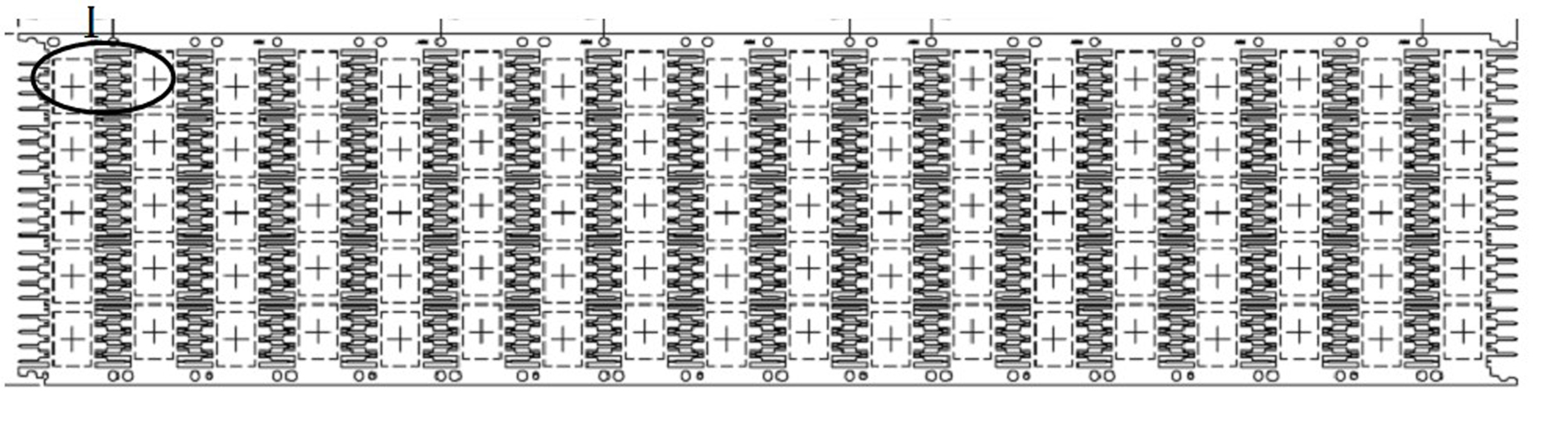

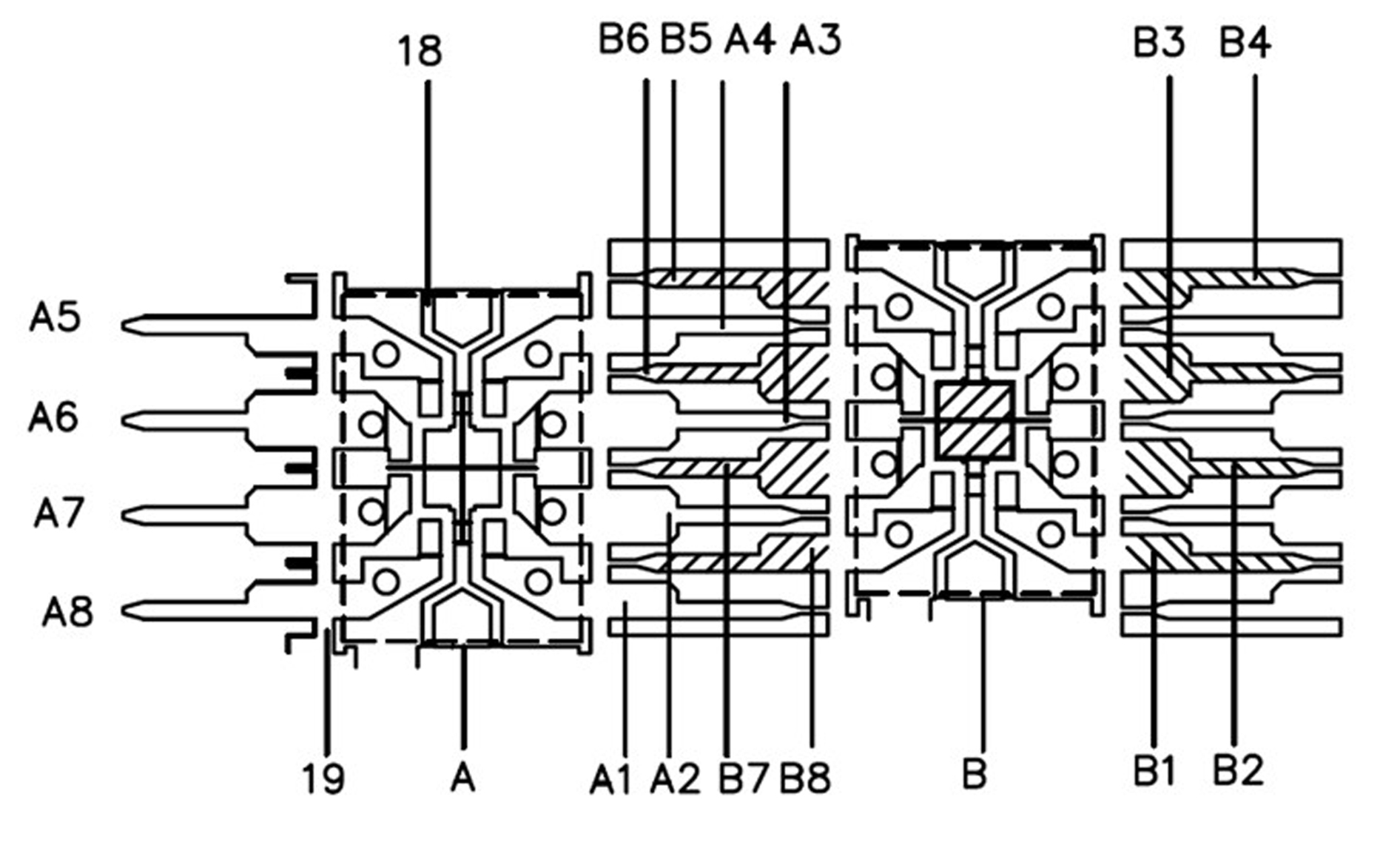

[0041] Embodiment 1, with reference to figure 1 , figure 2 , a single-carrier matrix DIP lead frame, the unit frame is a single-carrier structure and the number of rows is an odd number of rows, wherein the base islands of the adjacent unit frames of the 2n-1th row and the 2nth row are connected to the frame by connecting bars 18 The frames are connected, and the outer leads of the adjacent unit frames in row 2n-1 and row 2n are staggered, and are connected to the frame frames through grid bars 19 . For example: frame A unit and frame B unit are two adjacent unit frames, in which B8 is clamped between A1 and A2 lead pins, A2 is clamped between B8 and B7 lead pins, B7 is clamped between A2 and A3 lead pins A3 is clamped between the pins of B7 and B6, B6 is clamped between the pins of A3 and A4, A4 is clamped between the pins of B6 and B5, and so on.

Embodiment 2

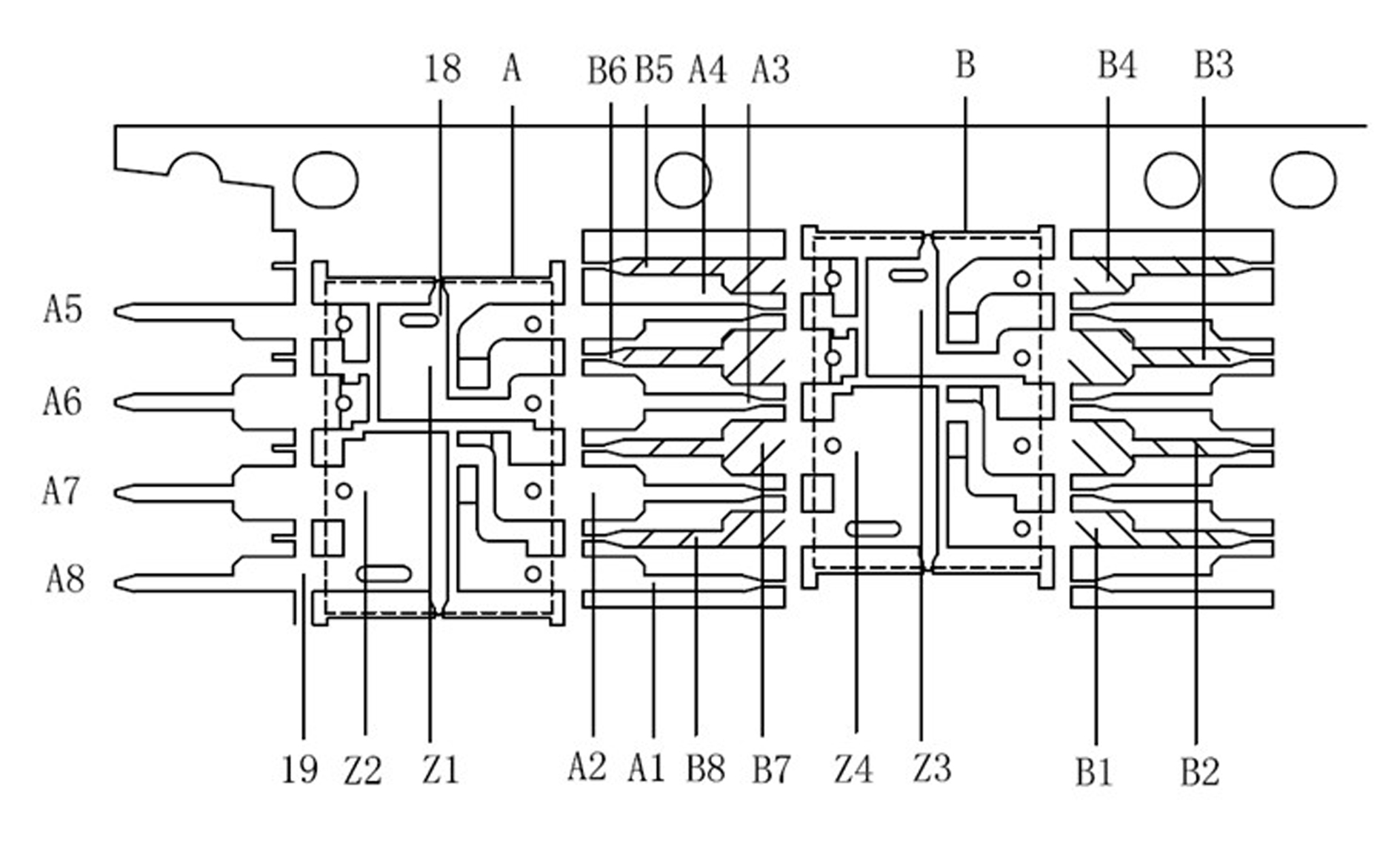

[0042] Embodiment 2, with reference to figure 1 , image 3, a double-carrier matrix DIP lead frame, the unit frame is a double-carrier structure and the number of rows is an odd number of rows, that is, each unit frame has 2 carriers; the pins A7 and A8 of the unit frame A are connected to the carrier Z2, lead The pin A3 is connected to the carrier Z1, the pins B7 and B8 of the adjacent unit frame B are connected to the carrier Z4, and the pin B3 is connected to the carrier Z3; the base island of the adjacent unit frame of the 2n-1 row and the 2n row The connecting bars 18 are connected to the frame frame, and the outer leads of the adjacent unit frames in the 2n-1 row and the 2n row are alternately arranged, and are connected to the frame frame through grid bars 19 . For example: unit frame A and unit frame B are two adjacent package units, in which B8 is clamped between the pins of A1 and A2, A2 is clamped between the pins of B8 and B7, and B7 is clamped between the pins of...

Embodiment 3

[0043] Embodiment 3, with reference to figure 1 , figure 2 , Figure 4 , a dual-chip IC package based on the unit frame of embodiment 1, comprising a carrier 1 on the unit frame, first and second IC chips 11, 12 are placed in parallel on the carrier 1 of the unit frame, the first On the pads on the IC chip 11 and the second IC chip 12, respectively pre-plant a gold wire or copper wire solder ball 10, and then use gold wire or copper wire on the gold wire or copper wire ball 10 of the first IC chip 11 Stacking gold wires or copper wire bonding balls, arching wire drawing arcs stacking gold or copper bonding balls on the gold or copper balls of the pads on the second IC chip 12 to form bonding balls 20, the bonding balls 20 make The first and second IC chips 11 and 12 are connected; the outer pads of the first and second IC chips 11 and 12 are connected to the inner pins 4 of the unit frame through copper or gold bonding wires 5 bonding; finally, plastic packaging The body 6...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com