SOI device resistant to total dose radiation and manufacturing method thereof

A technology of anti-total dose and manufacturing method, which is applied in the field of electronics, can solve problems such as deterioration of subthreshold slope, increase of power consumption of CMOS integrated circuits, and deterioration of device reliability, and achieve simple manufacturing process steps, wide application prospects, The Effect of Enhancing the Resistance to Total Dose Irradiation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] The present invention will be further described below through a specific preparation example in conjunction with the accompanying drawings.

[0025] This embodiment prepares the SOI device according to the present invention, and the preparation method mainly includes the following steps:

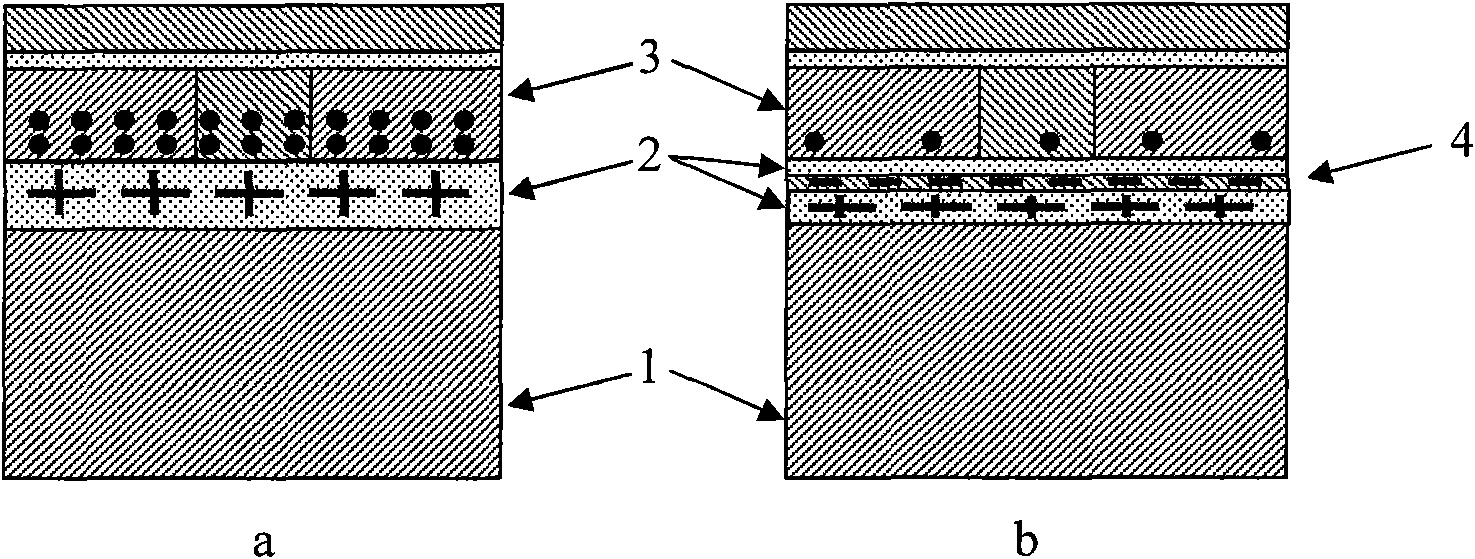

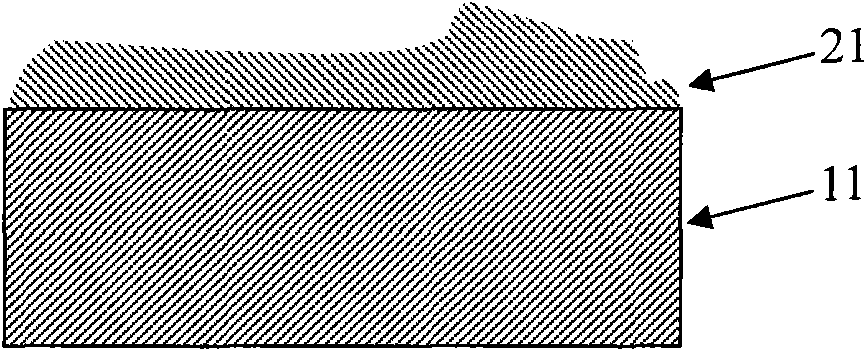

[0026] 1) if image 3 As shown, a silicon dioxide layer is grown on the silicon wafer 11 by a thermal oxidation growth method, that is, a buried oxide layer in the traditional sense, which is called the first SiO2 layer here. 2 Layer 21, the thermal oxidation temperature during the growth process is about 1050°C, and the thickness is about 60-70nm.

[0027] 2) if Figure 4 As shown, the first SiO 2 The surface of layer 21 is planarized so that its surface is as favorable as possible for the uniform deposition of subsequent deposition layers.

[0028] 3) if Figure 5 As shown, in the first SiO 2 On the polished surface of layer 21 is deposited a polysilicon sacrificial layer 4 wi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com