Chiral sensor and preparation method thereof

A sensor and chirality technology, applied in the field of sensors, can solve the problem that the detection accuracy of chiral substances cannot meet the actual needs of enantiomer identification, and achieve simple device structure and principle, diverse and flexible materials, reduced volume and cost effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

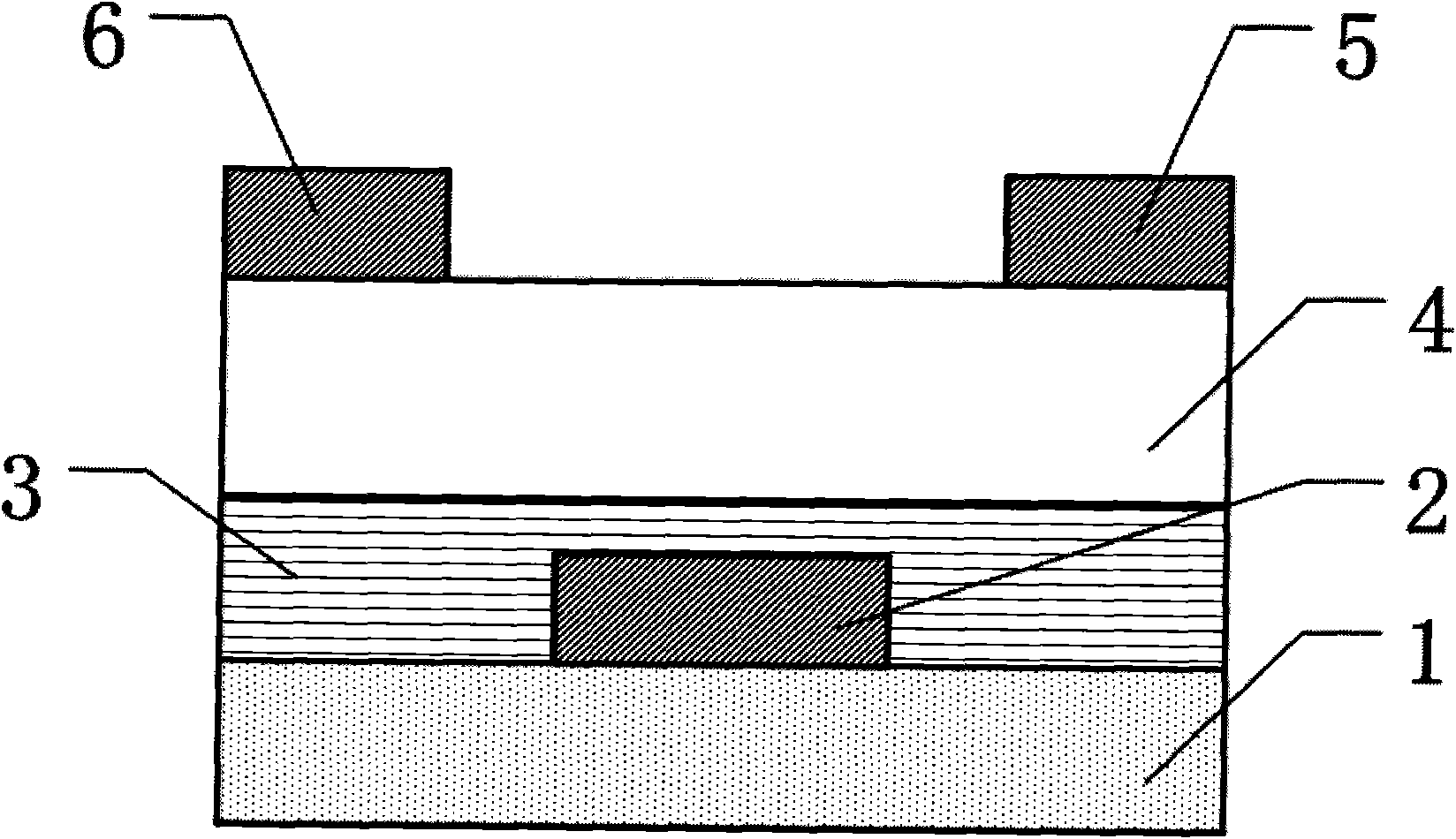

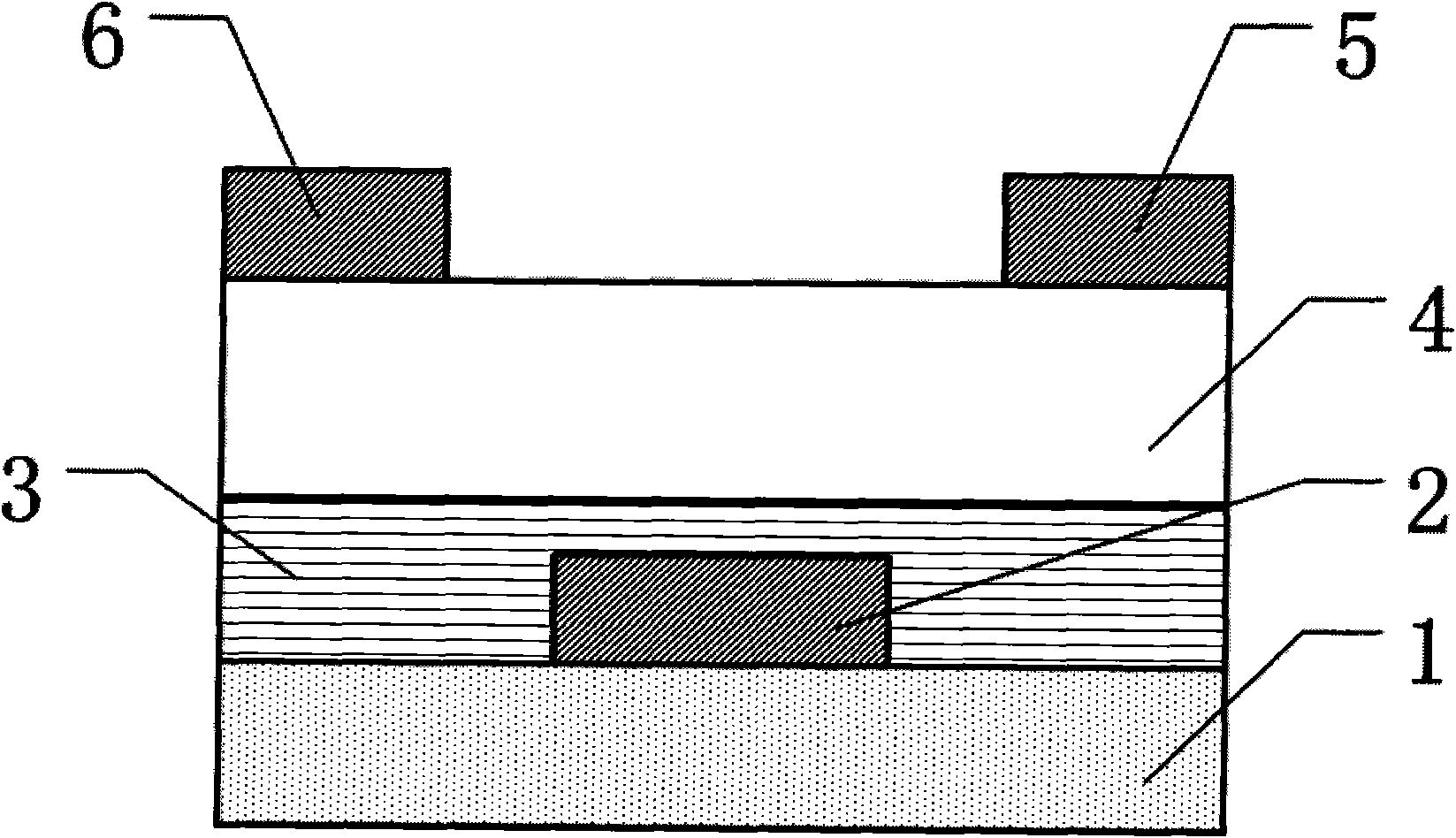

[0024] What is obtained by this preparation method is a bottom contact type chiral sensor:

[0025] Step 1: Sputtering or evaporating a layer of 10nm-500nm thick gate electrode 2 on the substrate 1. The gate electrode is composed of one or more of Ta, Ti, Cr, W, Mo, Au or Ag;

[0026] Step two, sputtering or evaporating a 150nm-500nm high dielectric constant gate insulating layer 3, the gate insulating layer 3 is made of SiO 2 , Ta 2 O 5 , Al 2 O 3 , TiO 2 , BZT or PZT one or two of them.

[0027] Step three, by vacuum thermal evaporation, spin coating, inkjet printing or screen printing a layer of 10nm-500nm thick active layer 4, the active layer 4 includes the following two different compositions (a), single chirality Organic semiconductors; (b) Chiral materials doped organic semiconductors.

[0028] Step 4: On the active layer 4, sputtering, inkjet printing or evaporating a layer of source electrode 5 and drain electrode 6 composed of one or two of Au, Ag, Ti, PEDOT:PSS, etc.

Embodiment 2

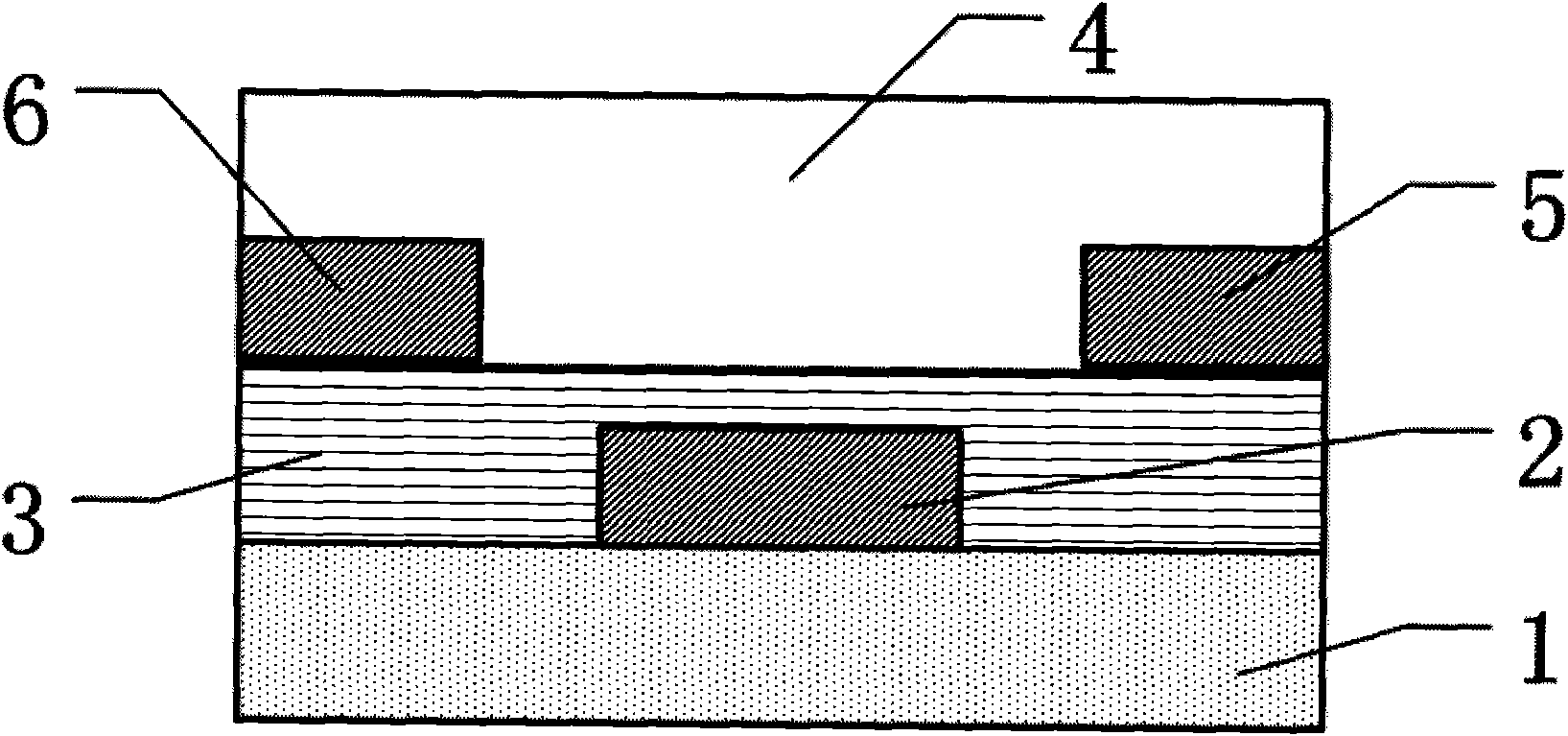

[0030] What is obtained by this preparation method is a top contact type chiral sensor:

[0031] Step 1: Sputtering or evaporating a layer of 10nm-500nm thick gate electrode 2 on the substrate 1. The gate electrode is composed of one or more of Ta, Ti, Cr, W, Mo, Au or Ag;

[0032] Step two, sputtering or evaporating a 150nm-500nm high dielectric constant gate insulating layer 3, the gate insulating layer 3 is made of SiO 2 , Ta 2 O 5 , Al 2 O 3 , TiO 2 , BZT or PZT one or two of them.

[0033] Step 3: On the gate insulating layer 3, sputtering, ink-jet printing or evaporating a layer of source electrode 5 and drain electrode 6 composed of one or two of Au, Ag, Ti, PEDOT:PSS, etc.

[0034] Step four, vacuum thermal evaporation, spin coating, ink-jet printing or screen printing on the gate insulating layer 3 and the source and drain electrodes is an active layer 4 with a thickness of 10nm-500nm, the composition of which can be selected as in the first embodiment.

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com