An asymmetric Schottky barrier MOS transistor and its manufacture method

A MOS transistor and Schottky potential technology, applied in the field of asymmetric Schottky barrier MOS transistors and their fabrication, can solve the problems of small on-state current, large off-state leakage, difficult integrated circuit applications, etc., and reduce complexity. performance, and the effect of reducing off-state leakage current

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0045] The following specific examples help to understand the characteristics and advantages of the present invention, but the implementation of the present invention is by no means limited to the described examples.

[0046] A specific embodiment of the manufacturing method of the present invention includes Figure 1 to Figure 8 Process steps shown:

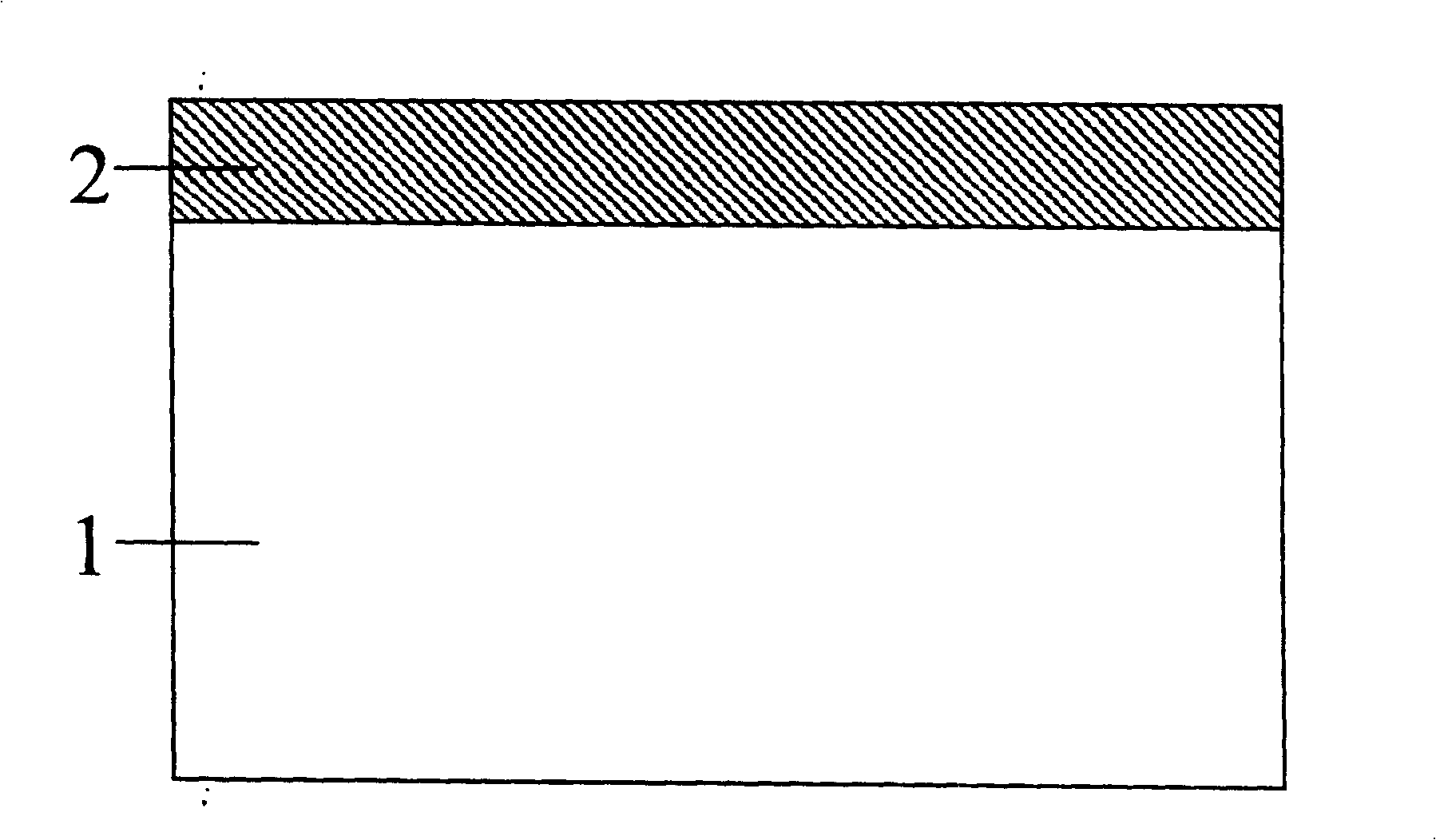

[0047] 1. If figure 1 As shown, the crystal orientation of the bulk silicon wafer silicon substrate (1) used is (100), the body region is initially lightly doped, and the active region isolation layer is fabricated on the substrate by using conventional CMOS shallow trench isolation technology; A layer of TEOS dielectric protection layer (2) is deposited with a thickness of 50-100 nm.

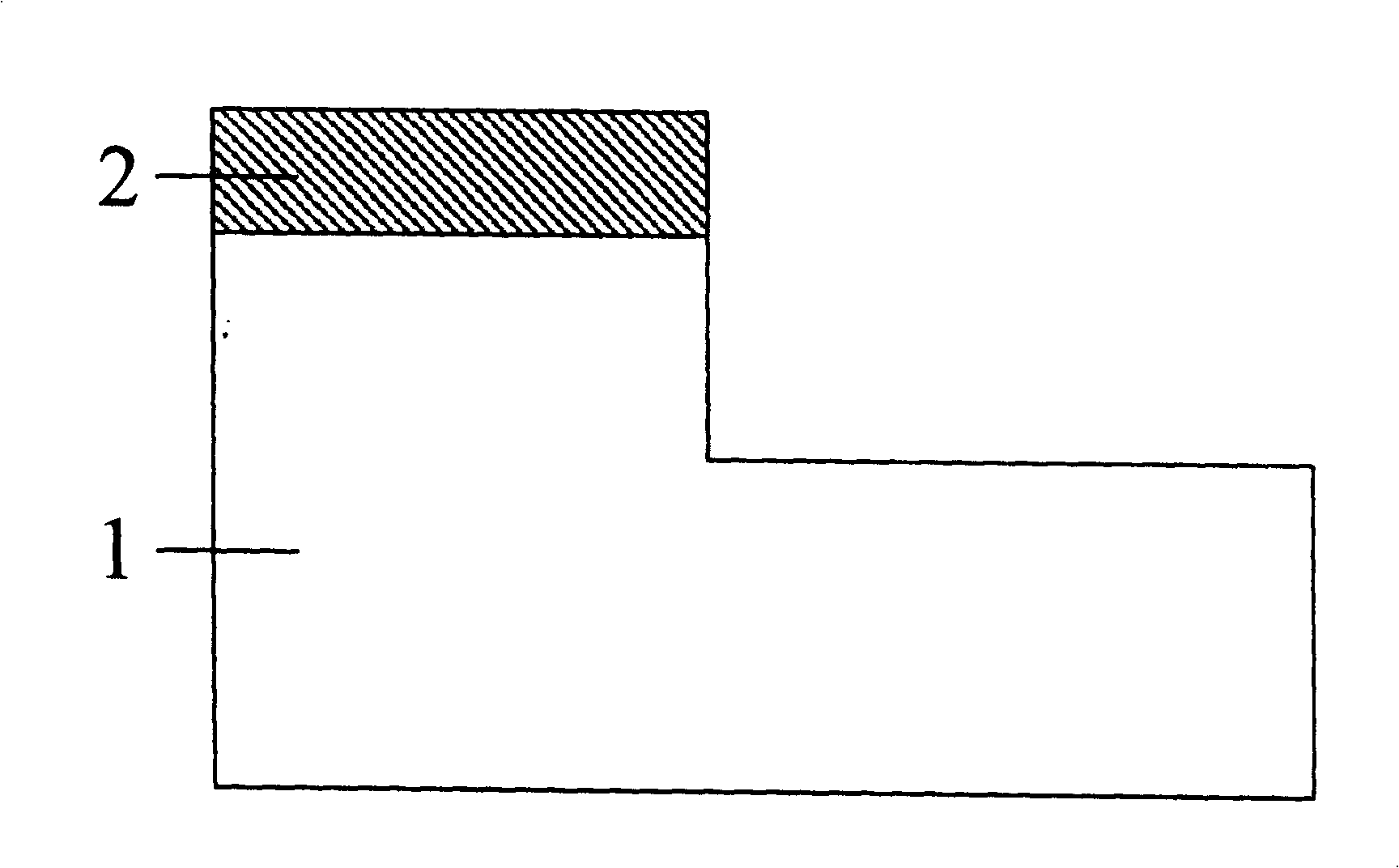

[0048] 2. If figure 2 As shown, photolithography is performed once to etch the TEOS dielectric protection layer (2), and then the unprotected silicon layer is etched to form a step structure, and the etching depth is 10-100nm.

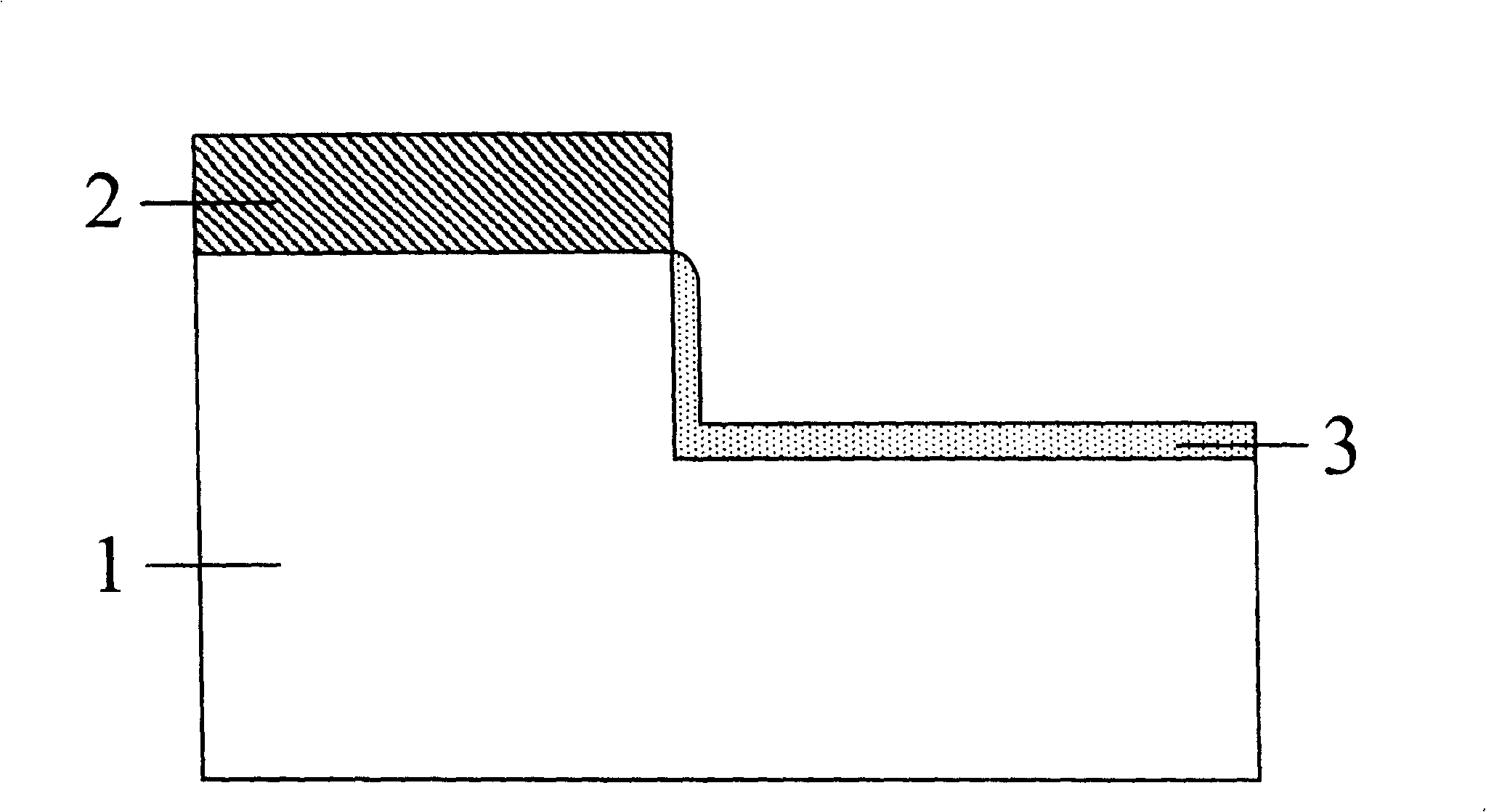

[0049] 3. If...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com