Semiconductor device and manufacturing method thereof

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

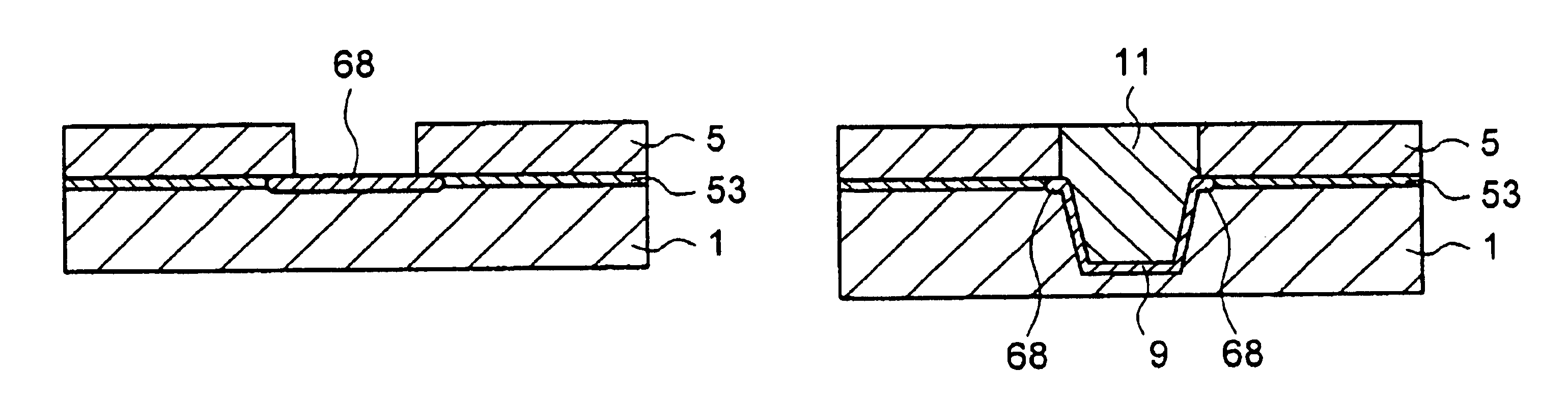

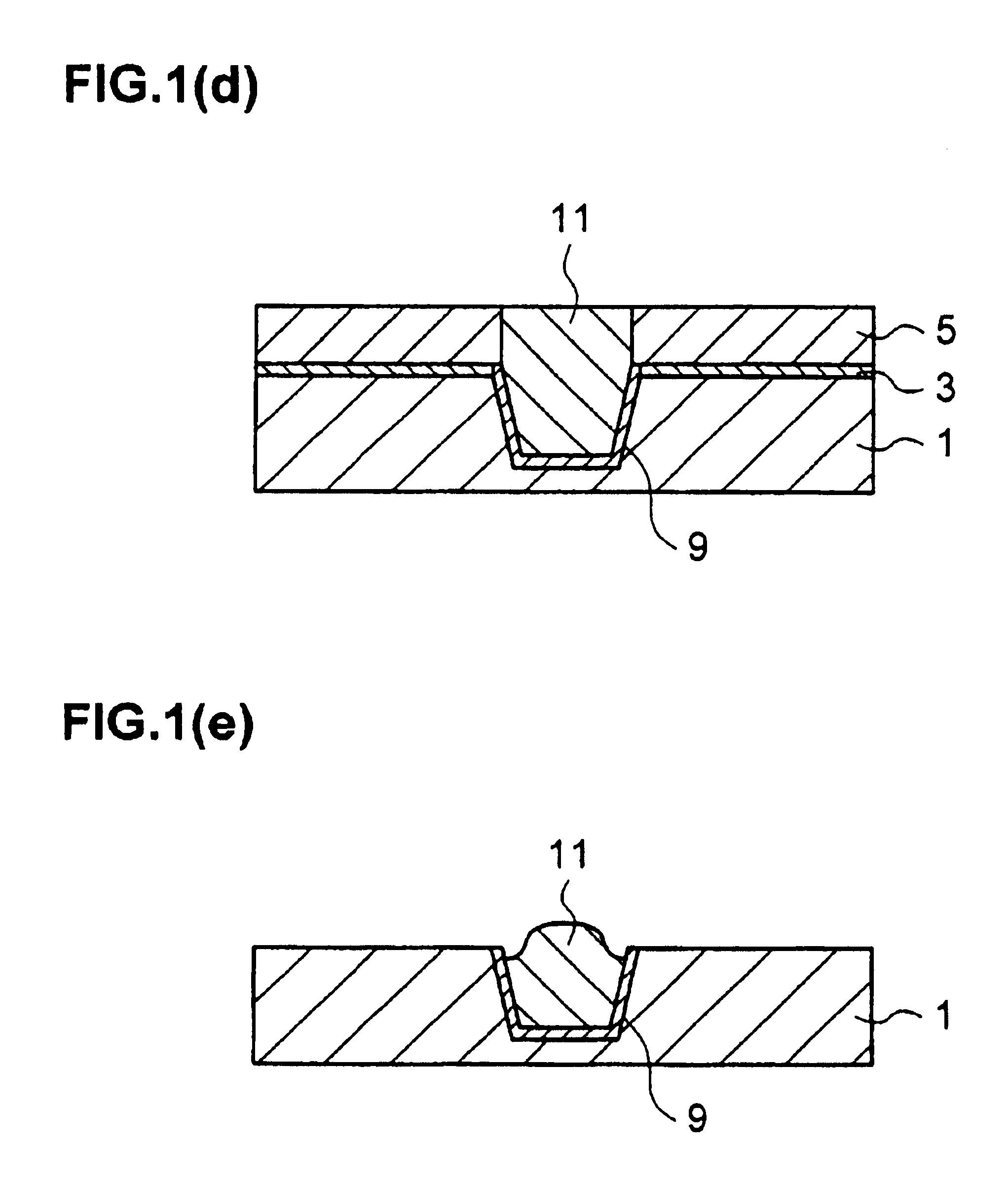

[0027]The following is a detailed explanation of the preferred embodiments of the present invention, given in reference to the drawings. FIG. 1 presents sectional views of the semiconductor device manufacturing steps in the present invention.[0028]1) First, as illustrated in FIG. 1(a), a pad oxide film 3 is formed to a thickness of 100-300 angstroms on an Si substrate 1 in a wet O2 atmosphere at 850 degrees centigrade. Over the pad oxide film 3 thus formed, an Si3N4 film 5 is formed to a thickness of 1500-2000 angstroms through LPCVD (low pressure CVD).[0029]2) Next, a photolithography process is performed and the Si3N4 film 5 is etched through the RIE (reactive ion etching) method. With a resist applied, the Si substrate 1 is etched by using the Si3N4 film 5 as a mask and the resist is removed to form a trench 7.[0030]3) As shown in FIG. 1(b), a trench liner oxide film 9 is formed to a thickness of 300 angstroms by employing the RTA (rapid thermal anneal) method in which oxidizing / ...

fifth embodiment

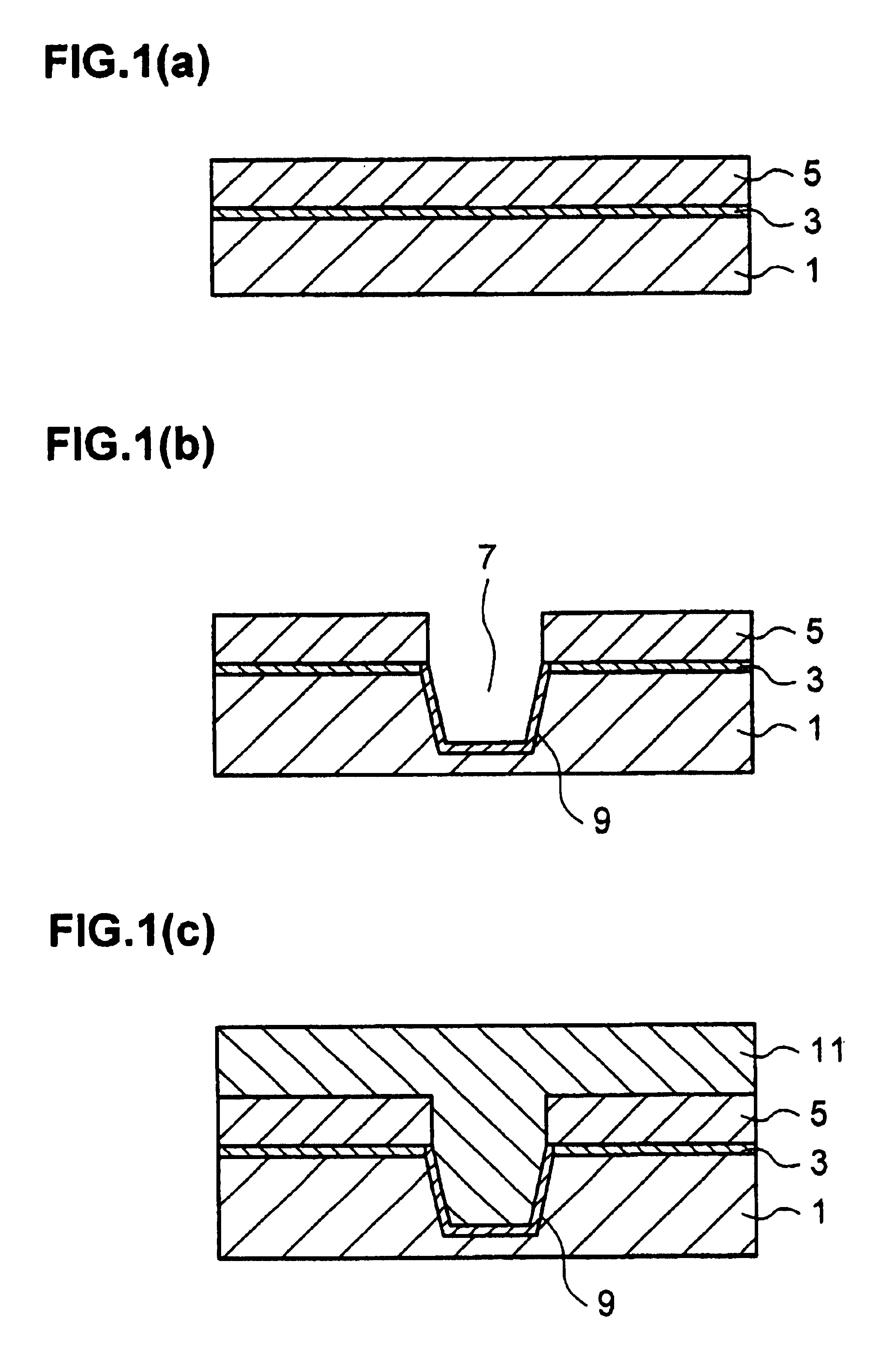

[0056]Next, the trench is filled with a CVD oxide film 11 and, as illustrated in FIG. 6(c), CMP is performed for planarization. As illustrated in FIG. 6(d), the S3N4 film 5 and the pad oxide film 53 are removed to form a field area. As shown in FIG. 6(e), a gate oxide film 48 is formed through oxidizing / nitriding as in the fifth embodiment, ion implementation is implemented to determine the transistor threshold voltage and activation annealing is performed. Then, specific steps are implemented to form a transistor.

[0057]During this process, the trench 7 may be formed after the sacrificial LOCOS 68 is formed by using the S3N4 film 5 as a mask without implementing the photolithography process. In such a case, since the photolithography process is skipped, the manufacturing method is simplified.

[0058]In this embodiment, since the remaining portion of the LOCOS 68 formed as a sacrifice constitutes an oxide film containing nitrogen, which acthieves a higher degree of HF resistance compar...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com