Semiconductor device, package structure thereof, and method for manufacturing the semiconductor device

a semiconductor and semiconductor technology, applied in the direction of semiconductor devices, semiconductor/solid-state device details, electrical devices, etc., can solve the problems of insufficient thinning, inability to use silicon substrates, and inability to easily thinne sip laminates, etc., to achieve easy laminated structure, easy to form thin films, and small thickness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

modified examples

[0079]Although there are various possible modified examples depending upon various laminated structures, a description will be made of an example in which two IC chips are mounted. A method for mounting a plurality of chips is an important technique for mixed mounting of ICs, for example, an analogue IC and a digital IC, which are difficult to form a monolithic type, to form a multifunctional SiP.

[0080]In this example, two IC chips are laminated to permit, compact mounting. This case has the problem with the method of forming connection between each of the chips and an electrode.

Modified Example 1

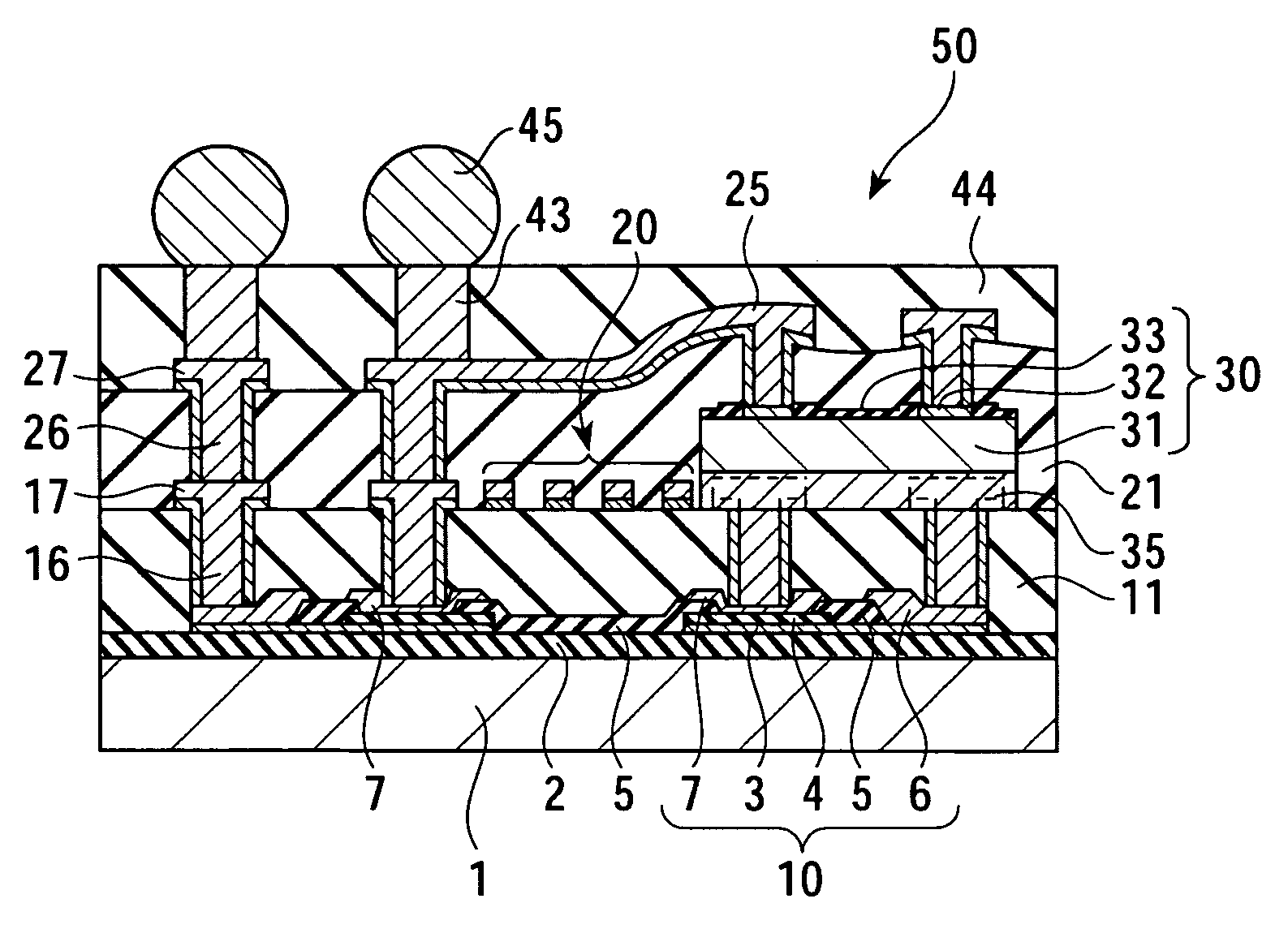

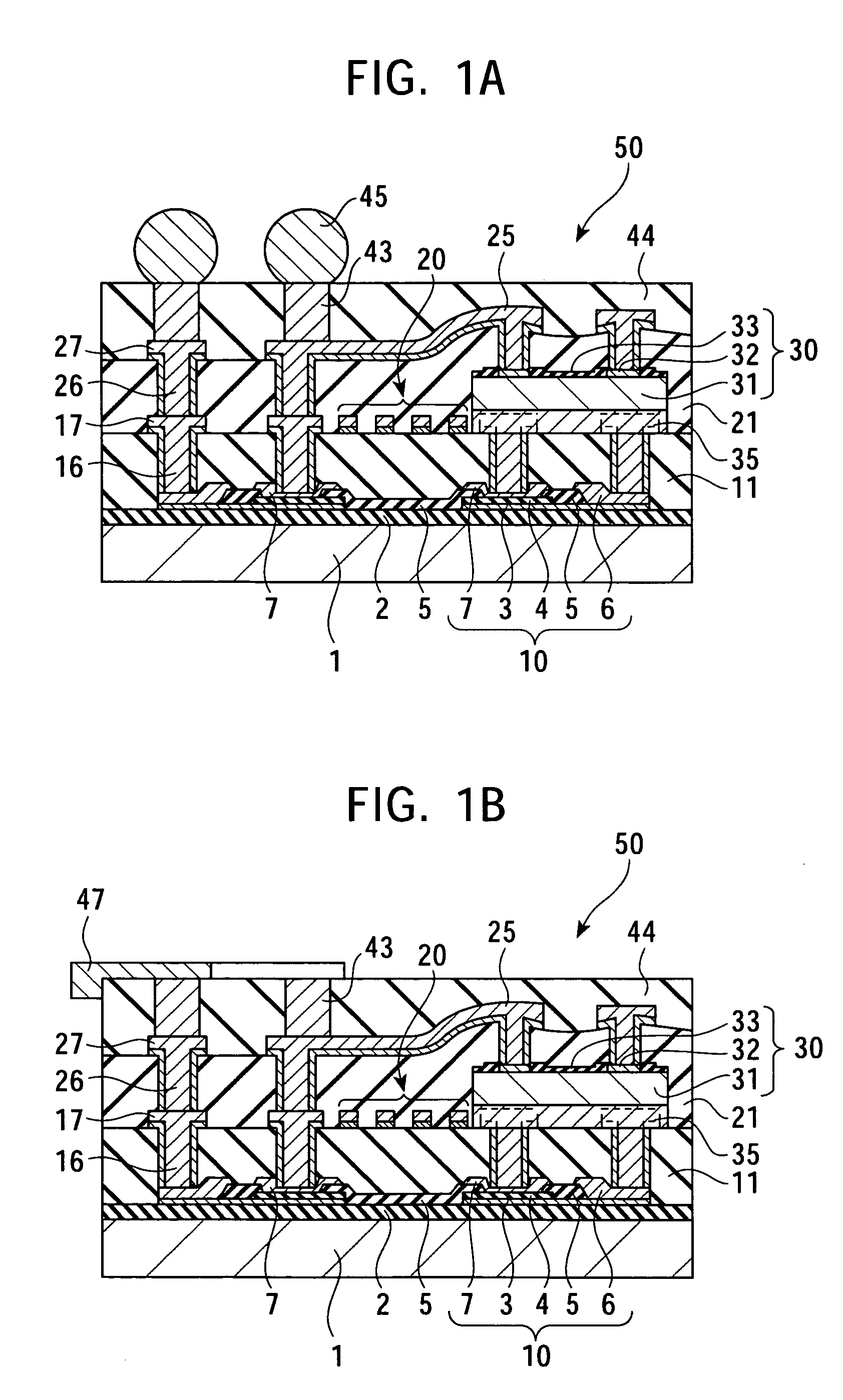

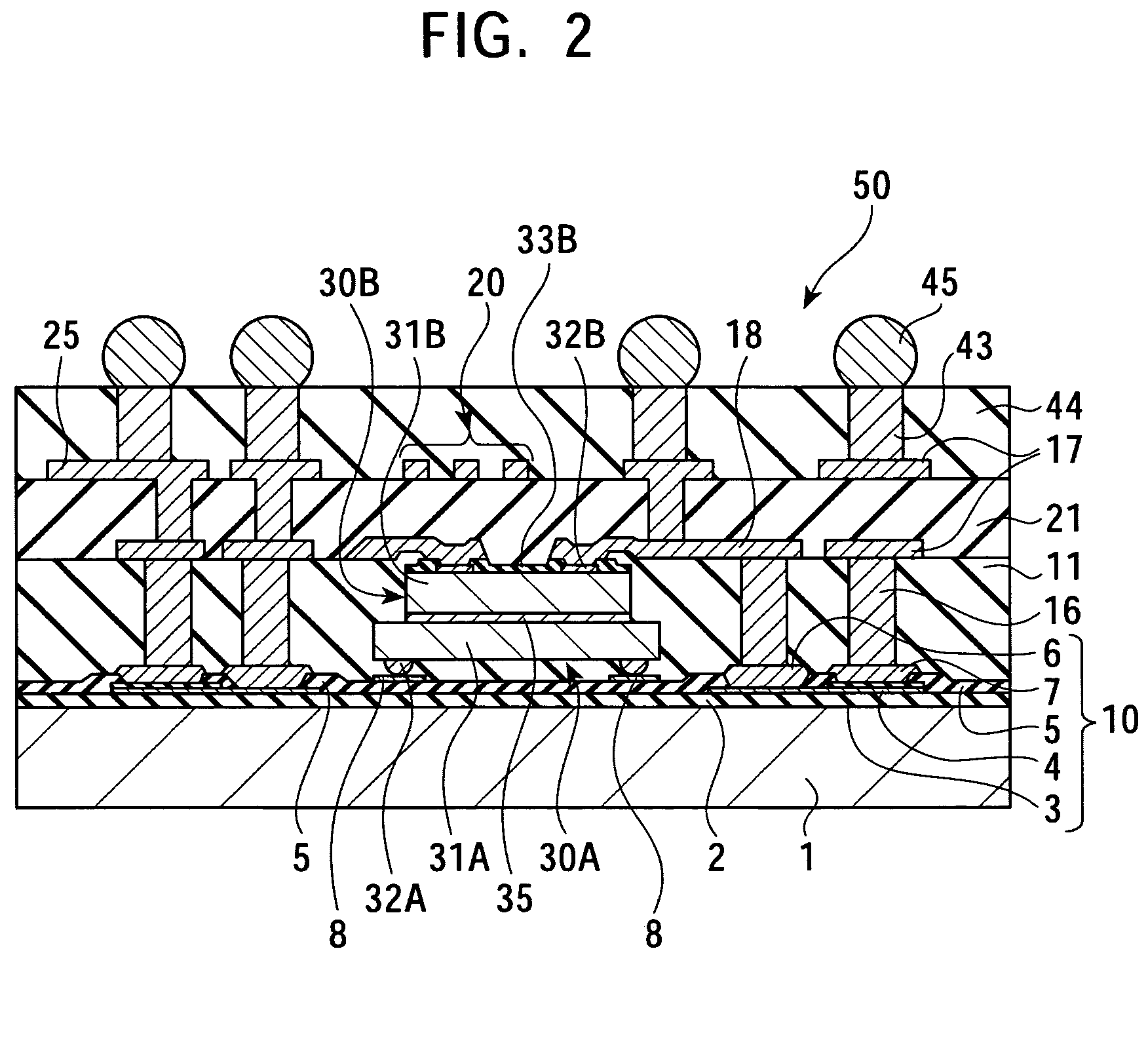

[0081]FIG. 2 is a schematic sectional view of a SiP in which a lower IC chip 30A is mounted in a face down state on the substrate 1, and an upper IC chip 30B is laminated and mounted in a face up state on the IC chip 30A. In the laminated structure of this example, the capacitor 10 and the IC chips 30A and 30B are covered with the first insulating layer 11, main wiring is covered with the s...

modified example 1

[0232]In order to amount the lower IC chip 30A in a face down state, as shown in FIG. 2, the substrate-side electrodes 8 to be bonded to the electrodes 32A of the IC chip 30A are formed on the protective layer 5 during the formation of the electrodes 6 and 7 of the capacitor 10. On the other hand, a Ni / Au, UBM, or Au stud bump or a solder bump for bonding is formed on each of the electrodes 32A of the IC chip 30A. Then, the silicon substrate 1 is aligned with the IC chip 30A, and the substrate-side electrodes 8 and the electrodes 32A are bonded together by heating under pressure.

[0233]The IC chip 30B is press-bonded to the IC chip 30A with the DAF provided on the electrode surface of the IC chip 30B at the back surface thereof, and fixed face up. This step is performed by heating at a temperature of 130° C. for 1 second with a load of 1 N / die.

[0234]Electric connection to the IC chip 30B mounted face up is formed by the basic method of the above-described embodiment in which one IC c...

modified example 2

[0235]As shown in FIGS. 3A and 3B, when the IC chips 30A and 30B are mounted in a face up state, X, Y and Z-direction deviations between the chips and an inclination θ between the chips must be decreased. Also, the gap between the chips must be filled with a resin which little causes a step and air bubbles in the gap.

[0236]In this case, electric connection to the upper IC chip 30B is performed by the basic method described in the above embodiment. Namely, plugs are formed in an insulating layer which covers the IC chip 30B to be connected to electrodes, and a conductive layer is formed on the surface of the insulating layer.

[0237]When wiring to be connected to the IC chip 30A need not be separately provided, electric connection to the lower IC chip 30A is formed together with the electric connection to the upper IC chip 30B, as shown in FIG. 3B. When wiring to be connected to the IC chip 30A must be separately provided, as shown in FIG. 3A, the intermediate insulating layer 28 is fo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com