High voltage MOS transistor with up-retro well

a high-voltage mos transistor and up-retro well technology, which is applied in the direction of semiconductor devices, semiconductor/solid-state device details, electrical apparatus, etc., can solve the problems of increasing the electric field under the gate, undesired current flow between the drain and the buried layer, and the dmos transistor b>10/b> to have undesired large device dimensions, etc., to achieve the effect of low threshold voltag

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

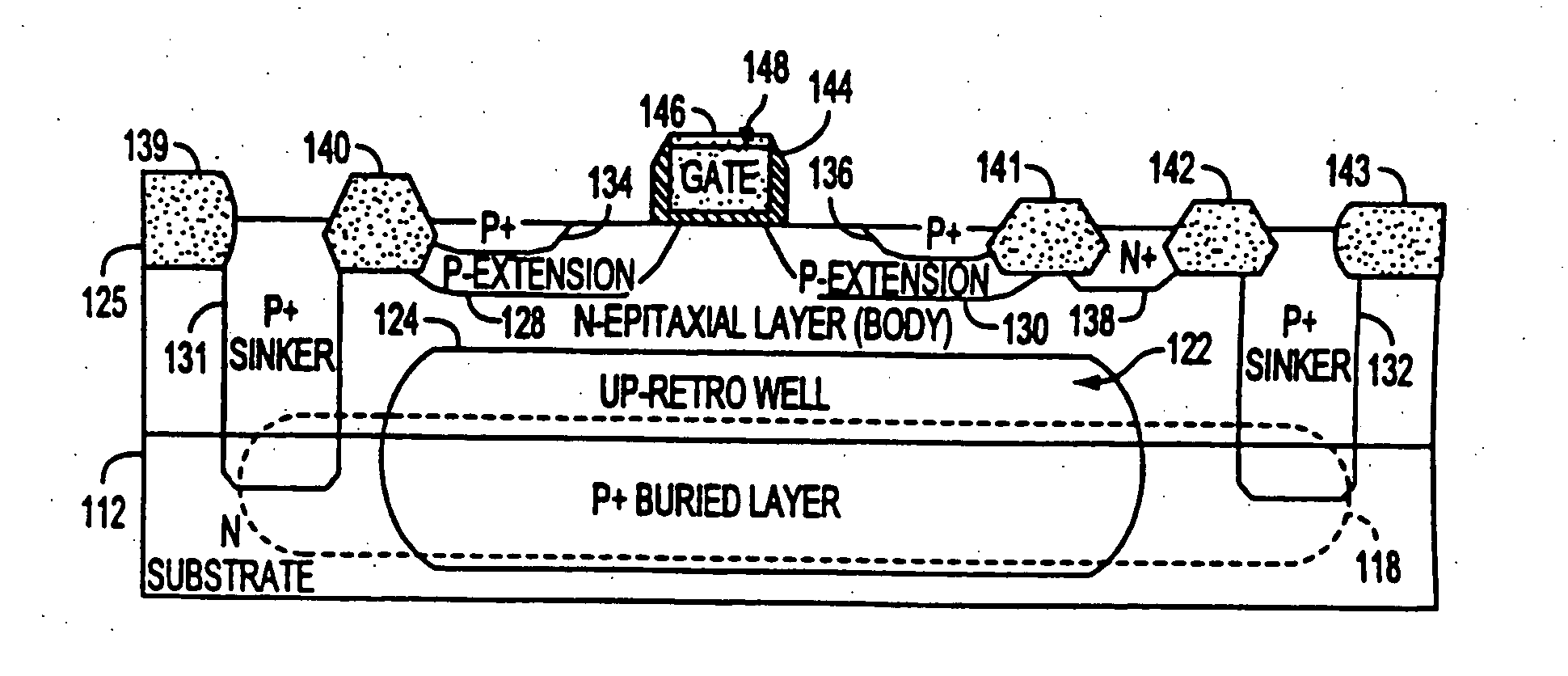

[0034] Process steps for an illustrative embodiment of a high voltage MOS transistor with an up-retro well are shown in FIGS. 3A-3F. In this embodiment, an NMOS transistor is formed in a P-type epitaxial layer on a P-type substrate. A highly doped N+ buried layer is formed in the P-substrate to isolate the P-epitaxial layer and the P-substrate. The NMOS transistor has a P-type up-retro well that is formed from dopants implanted into the substrate. The up-retro well P-type dopants diffuse into the P-epitaxial layer (farther than the N-type buried layer dopants) when the epitaxial layer is formed and during subsequent heating steps. The P-type up-retro well dopants increase the net concentration of P-type dopants in the region of the P-epitaxial layer into which the up-retro well dopants diffuse. The region of increased net P-type doping concentration is above the epitaxy-substrate interface. The up-retro well dopants allow the epitaxial layer to be made relatively thin. The increased...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com