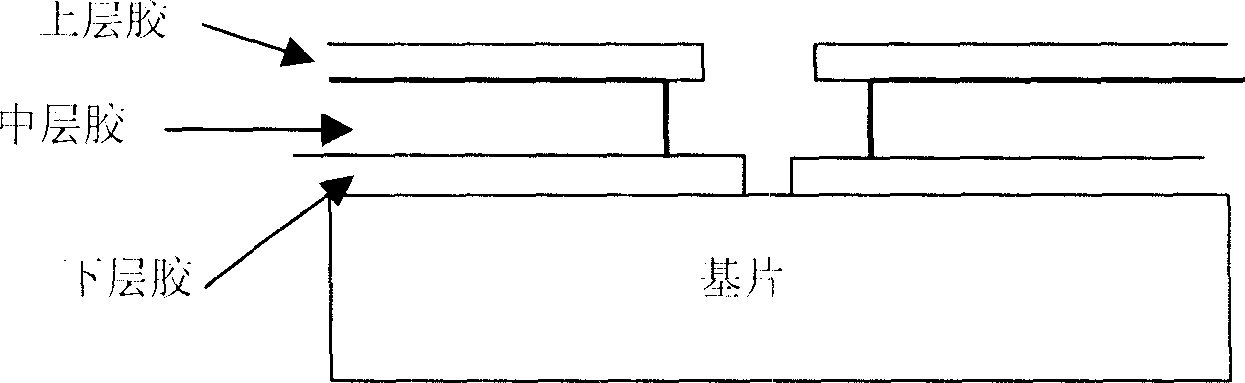

Method for making T-type grating of transistor circuit with high electron mobility

A technology with high electron mobility and manufacturing method, which is applied in the field of ultra-high-speed microelectronic devices, can solve the problems of increasing process steps, and achieve the effects of simplifying process steps, strong controllability, and easy peeling

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

[0061] Embodiment: On the compound semiconductor experimental line of the Microelectronics Center of the Chinese Academy of Sciences, gallium arsenide (GaAs)-based MHEMT and indium phosphide (InP)-based devices were fabricated, and the method of the present invention was used to expose and develop the grid , a T-shaped gate with a gate length of 122 nanometers was obtained, and a device with good performance was obtained.

[0062] figure 2 It is a photo of the device actually produced.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com