Chip wafer-level packaging structure of micro electro mechanical system and manufacturing process of chip wafer-level packaging structure

A micro-electro-mechanical system and wafer-level packaging technology, which is applied in the direction of micro-structure technology, micro-structure devices, and manufacturing micro-structure devices, can solve the problems that affect the performance of micro-electro-mechanical systems, can not effectively reduce the impact of packaging stress, Young's modulus and Problems such as thermal expansion coefficient mismatch

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0040]The present invention will be described in detail below in conjunction with the embodiments and the accompanying drawings. It should be noted that the described embodiments are only intended to facilitate the understanding of the present invention, rather than limiting it in any way.

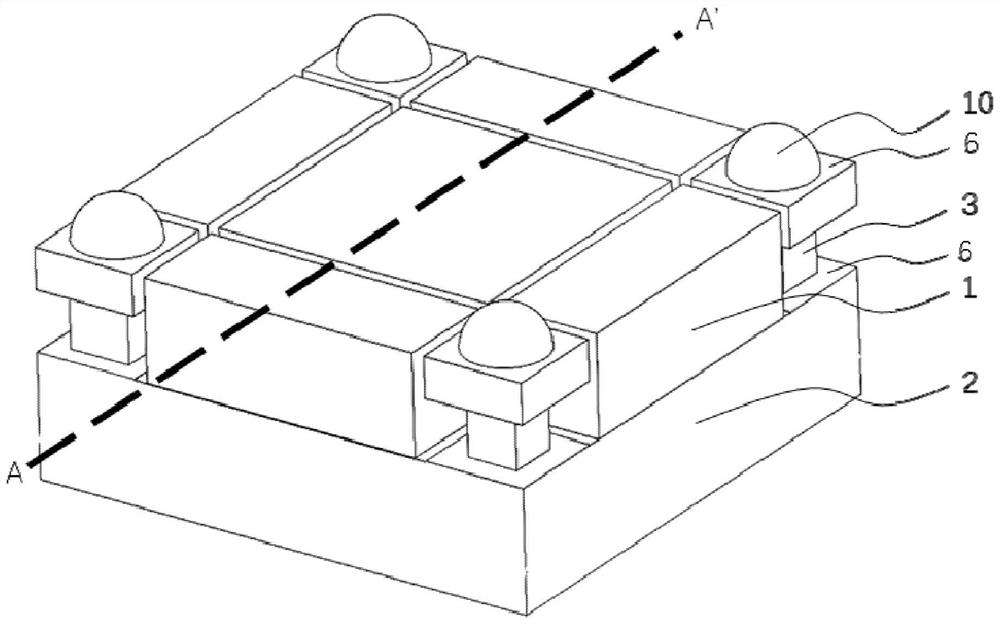

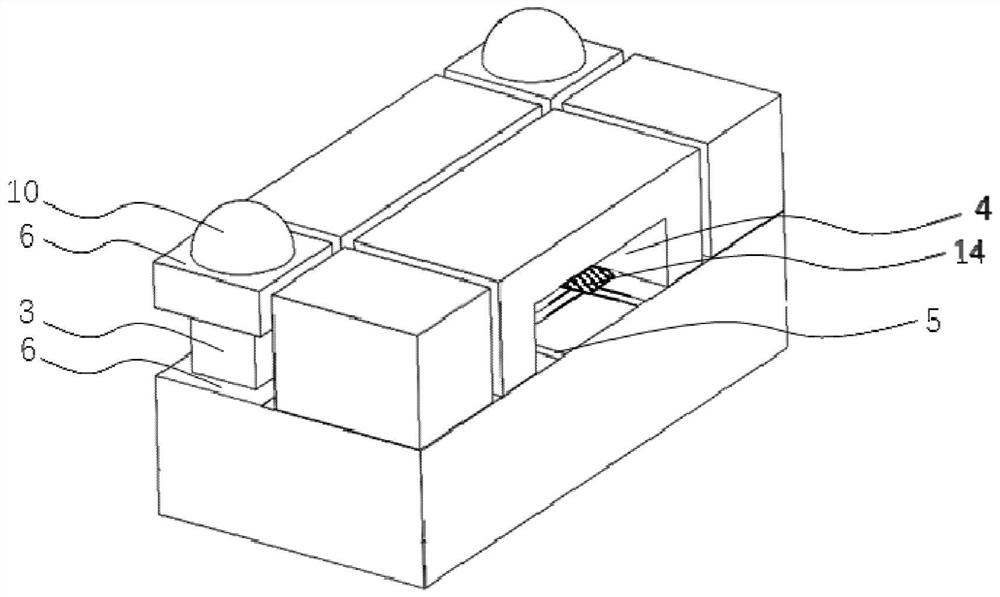

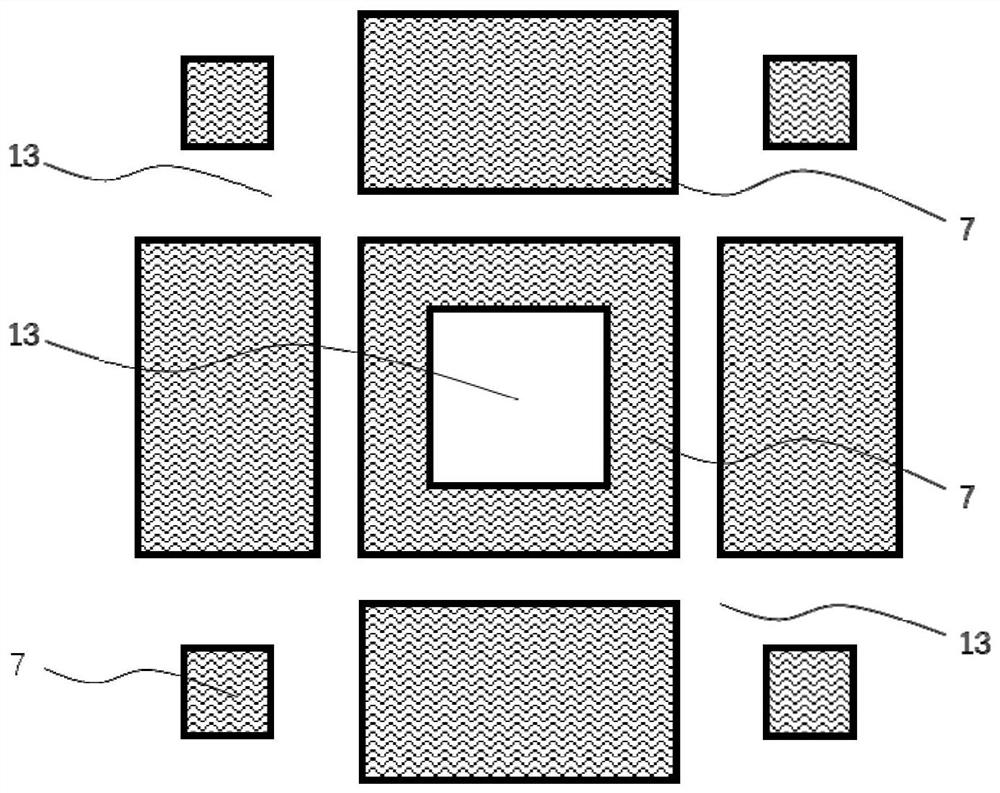

[0041] refer to figure 1 , figure 2 , according to an embodiment of a MEMS chip wafer level package provided by the present invention. In this embodiment, the cover plate 1 and the substrate 2 are bonded to each other. The cover plate 1 is usually made of monocrystalline silicon. The substrate 2 can be selected to use a single crystal silicon wafer, an SOI silicon wafer, etc. according to the final chip structure and manufacturing process. Wherein, a recessed portion 13 is formed on one side of the cover plate 1 , and a cavity is formed between the recessed portion 13 and the substrate 2 after the cover plate 1 and the substrate 2 are bonded. A plurality of micro-electromechanical ele...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com