TSV-based three-dimensional integrated circuit packaging method

A technology of integrated circuits and packaging methods, applied in circuits, electrical components, electrical solid devices, etc., can solve the problems of micro-cracks on the surface of wafers, easy generation of debris, and influence of chip thermo-mechanical reliability.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] In order to have a clearer understanding of the technical features, purposes and effects of the present invention, the specific implementation manners of the present invention will now be described with reference to the accompanying drawings.

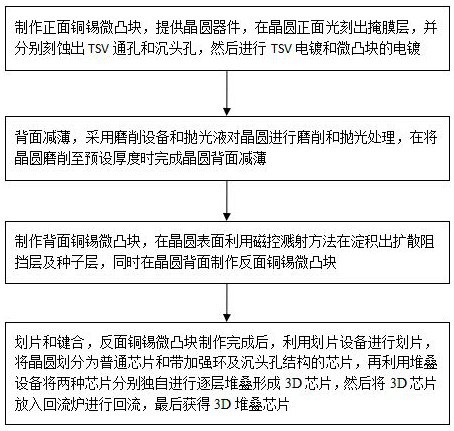

[0033] In this example, if figure 1 As shown, a TSV-based three-dimensional integrated circuit packaging method, the method specifically includes: Step 1: making front copper-tin micro-bumps, providing wafer devices, photoetching a mask layer on the front of the wafer, and etching out TSV through holes and countersunk holes, and then TSV electroplating and electroplating of micro-bumps; Step 2: Backside thinning, grinding and polishing the wafer with grinding equipment and polishing liquid, and grinding the wafer to Thinning of the back of the wafer is completed when the thickness is preset; step 3: making micro-bumps of copper and tin on the back, and depositing a diffusion barrier layer and a seed layer on the surface of the wa...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com