Manufacturing method of backside illuminated and electronic impact type CMOS sensors, pixel and sensor

A technology of CMOS sensor and manufacturing method, which is applied in the direction of electric solid-state devices, circuits, electrical components, etc., can solve the problems such as offset, increase of deviation, and no record of analog circuit characteristics that are not recorded.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 approach

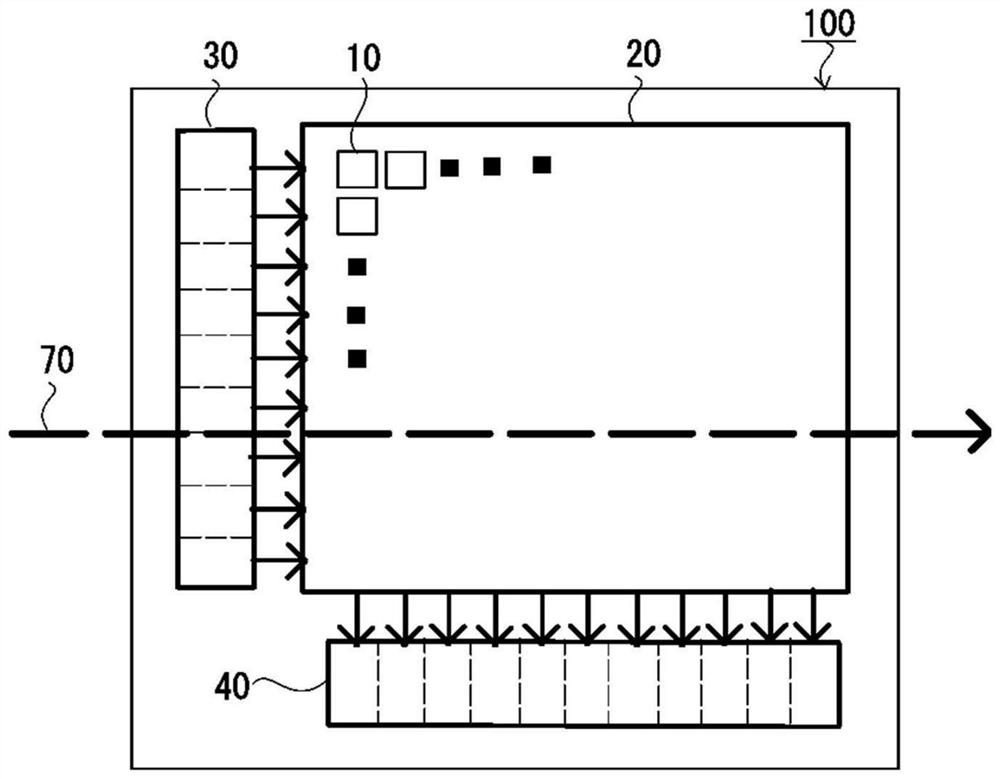

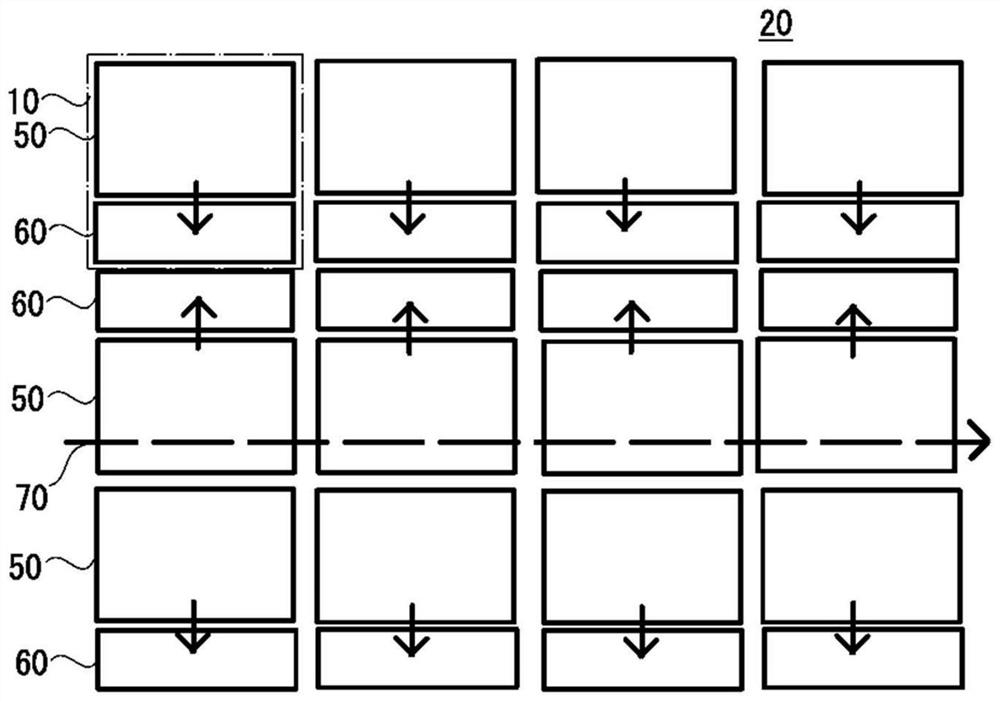

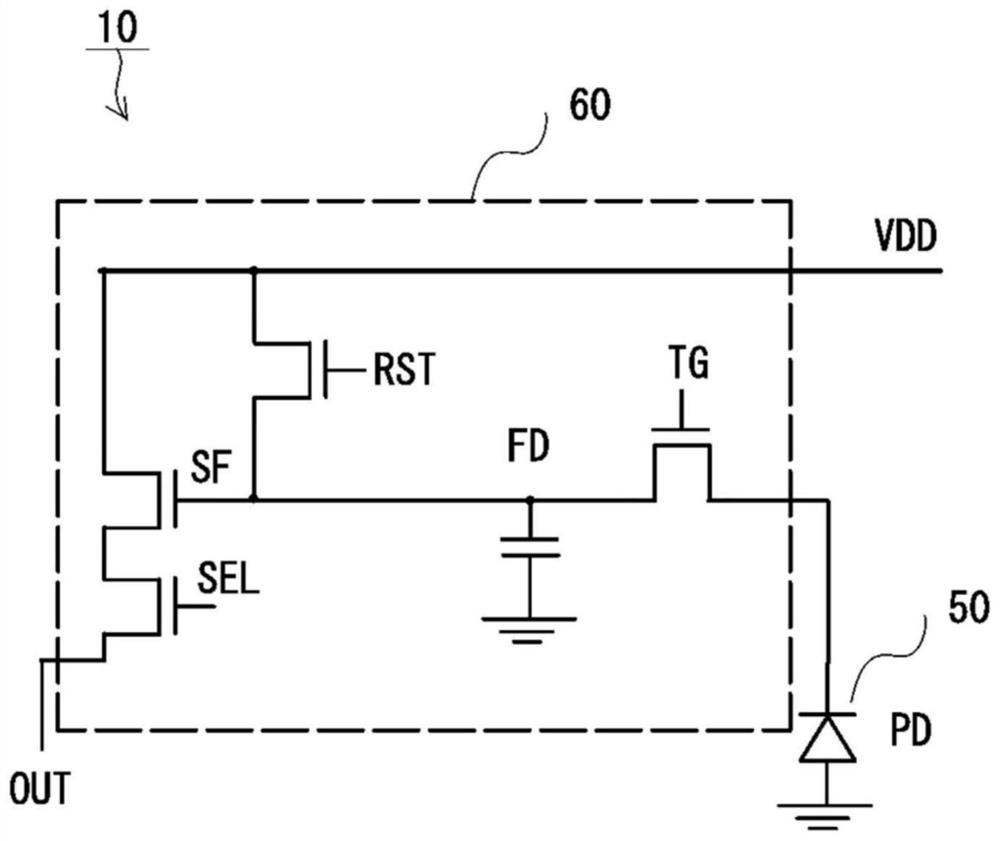

[0158] figure 1 is a schematic plan view of the back-illuminated CMOS sensor 100 of the first embodiment viewed from the front side, figure 2 is a schematic plan view showing an example of the arrangement of the photosensitive region 50 and the readout circuit 60 in the pixel region 20 of the back-illuminated CMOS sensor 100, image 3 is a schematic circuit diagram showing the structure of a pixel 10 of a back-illuminated CMOS sensor 100, Figure 4 is a schematic cross-sectional view around the photosensitive region 50 of the back-illuminated CMOS sensor 100 .

[0159] (Configuration of back-illuminated CMOS sensor 100 )

[0160] figure 1 An example of the overall configuration of the back-illuminated CMOS sensor 100 is shown. The back-illuminated CMOS sensor 100 is composed of a pixel area 20, a digital circuit 30 (vertical selection circuit, etc.) and an analog circuit 40 (sample-and-hold circuit, AD converter, etc.), and in the pixel area 20, the pixels 10 are horizont...

no. 2 approach

[0193] Figure 5 It is a schematic diagram showing the relationship between the position of the void 130 in the silicon wafer 110 and the laser irradiation region 120 in the second embodiment.

[0194] In general, the back-illuminated CMOS sensor 100 improves physical strength by bonding the surface side of the silicon wafer 110 on which the photosensitive region 50 or the readout circuit 60 and the like are formed to a silicon wafer serving as the supporting substrate 310 . However, when the silicon wafers are bonded together, voids 130 (voids) are generated at the bonding interface. In particular, at the wafer perimeter, particles attach, and small air bubbles are enclosed along the wafer perimeter, creating more voids 130 .

[0195] Furthermore, when the laser beam is irradiated to the part of the cavity 130 where the wafer is bonded, the gas etc. enclosed in the cavity 130 will expand rapidly, and the periphery of the cavity 130 will be in an explosive state, and silicon ...

no. 3 approach

[0201] Figure 6 It is a graph showing the difference in the distribution of ion-implanted boron depending on the presence or absence of an oxide film.

[0202] The manufacturing method of the back-illuminated CMOS sensor 100 according to the third embodiment relates to a method of implanting boron ions into the back surface of the back-illuminated CMOS sensor 100 .

[0203] Such as Figure 4 As shown, a P+ diffusion layer 270 is formed on the back surface (light-incident surface) of the photosensitive region 50 . This is to make the electrons of the electron-hole pairs generated at the interface on the back surface disappear by recombination with the holes in the P+ diffusion layer 270 so as not to become dark current.

[0204] On the other hand, when incident photons are photoelectrically converted inside the P+ diffusion layer 270 , the back-illuminated CMOS sensor 100 cannot detect the photons. In addition, when the back-illuminated CMOS sensor 100 is used as the sensor...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com