Low-power-consumption external interrupt wake-up circuit and control method thereof

An external interrupt and wake-up circuit technology, applied in the direction of reducing power consumption, logic circuit, logic circuit connection/interface layout, etc., can solve the problem of increasing the scale of digital codes and digital logic complexity, and cannot use traditional processing methods. Edge detection, increase Constant power supply digital logic power consumption and other issues, to achieve the effect of small quantity, small occupied layout area, and few types of devices

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0039] A preferred embodiment of the present invention will be described in detail below with reference to the accompanying drawings.

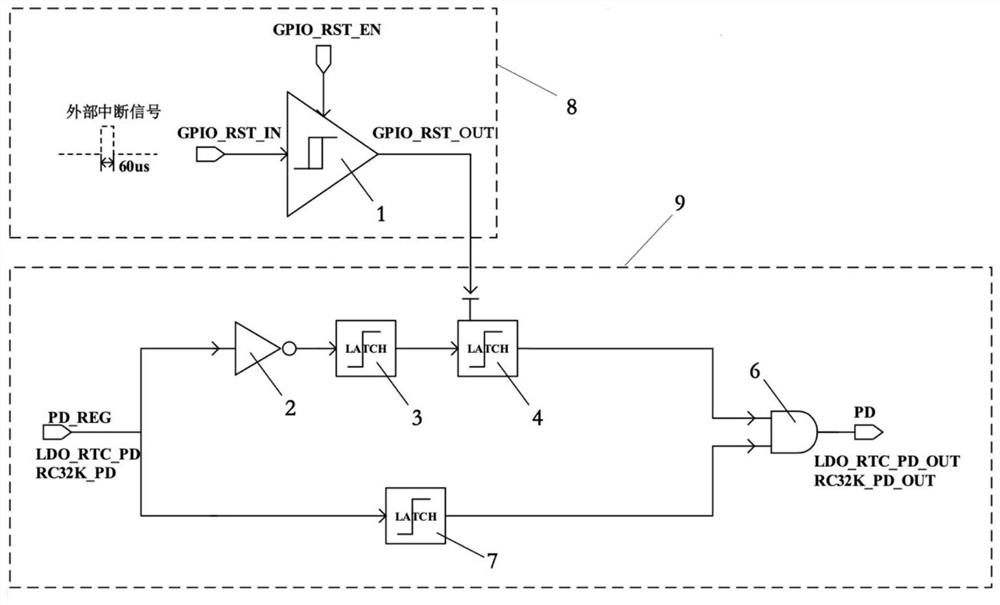

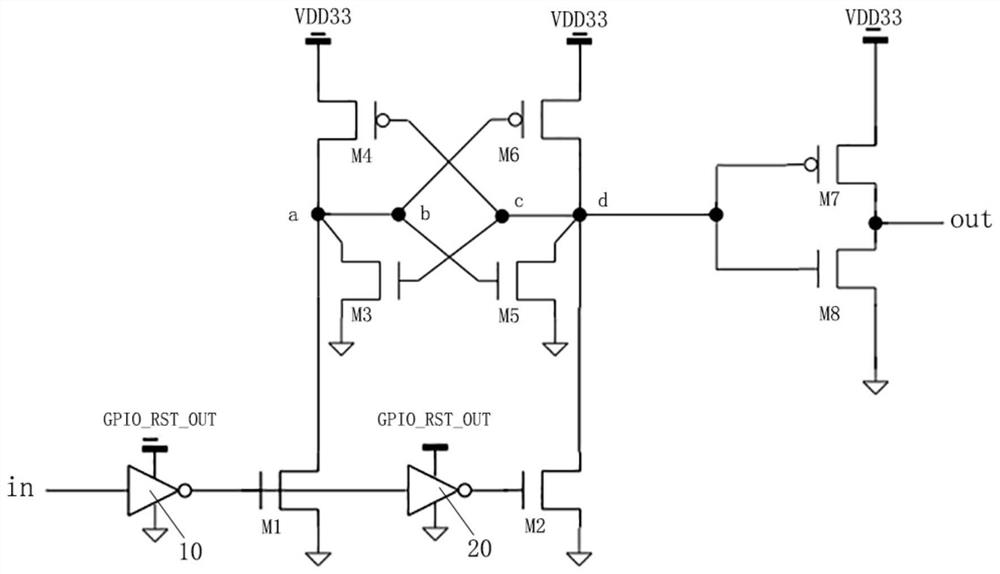

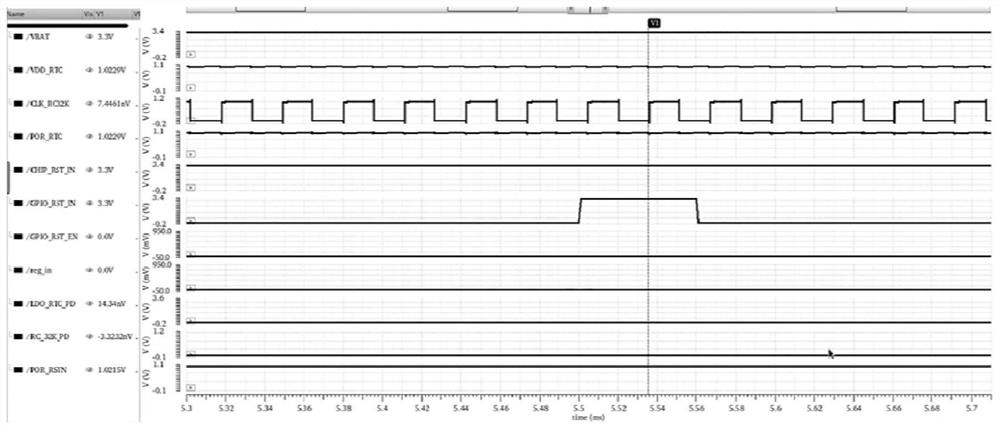

[0040] The present invention aims to propose such a low-power external interrupt wake-up circuit. Since the circuit works in a deep sleep state, there is no clock and no power supply. It is necessary to break through the idea of digital dominant participation in edge detection in the traditional reset circuit and introduce a new wake-up method. The circuit principle does not require the leading participation of digital logic, and the external interrupt excitation forces the analog circuit part to forcibly turn on the power supply and clock, thereby resetting the entire chip circuit. Compared with the button reset signal, the external interrupt signal lasts for a shorter high level time, generally only a few clock cycles, which means that the wake-up circuit must be able to accept the extremely short duration of the external interrupt pulse, a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com