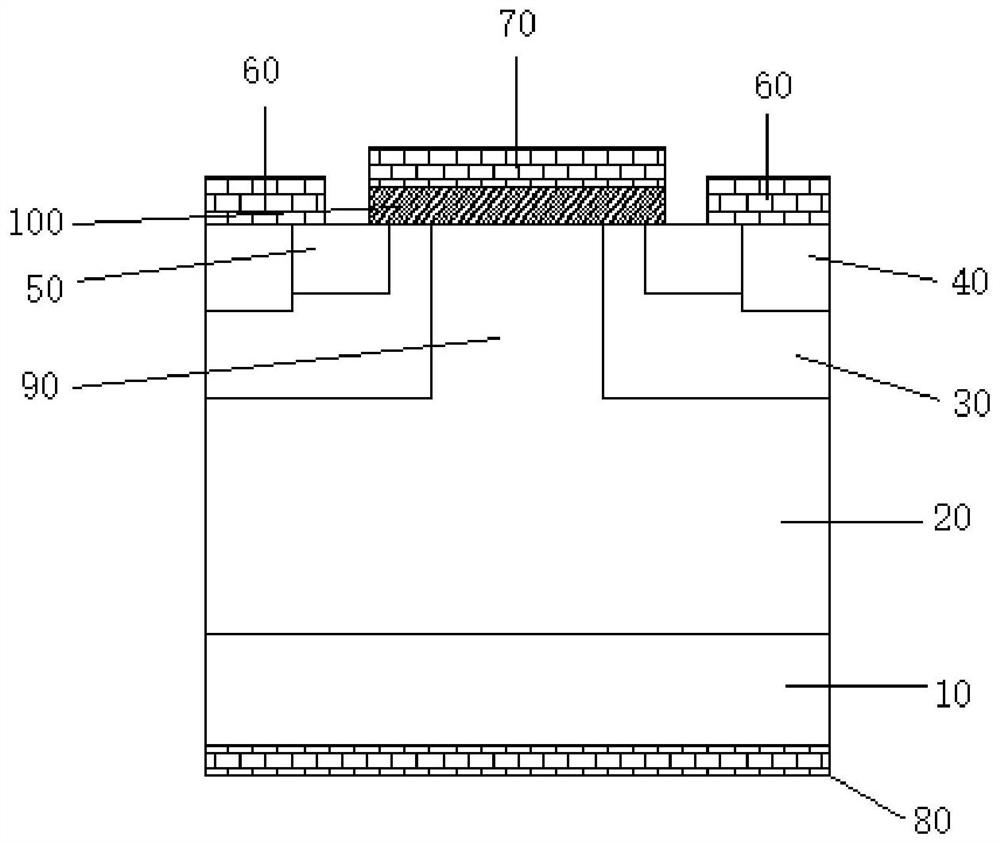

vdmosfet and its preparation method and semiconductor device

A conductive type, lightly doped technology, applied in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve problems such as low device withstand voltage, low interface state density, channel mobility, gate oxide breakdown, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

[0055] The method can quickly and effectively prepare and obtain the aforementioned VDMOSFET, has simple steps, is convenient to operate, and is easy to realize industrial production.

[0056] In yet another aspect of the present application, the present application provides a semiconductor device. According to an embodiment of the present application, the semiconductor device includes the aforementioned VDMOSFET. The semiconductor device includes all the features and advantages of the above-mentioned VDMOSFET, which will not be repeated here.

[0057] According to the embodiment of the present application, the specific type of the semiconductor device can be MOSFET (Metal-Oxide Semiconductor Field Effect Transistor), IGBT (Insulated Gate Bipolar Transistor), and those skilled in the art can understand that, in addition to the aforementioned In addition to the VDMOSFET, and including the necessary structures and components of conventional devices, details will not be repeated...

Embodiment 1

[0060] Step 1: Epitaxially form an N-type SIC doped layer 8 on a heavily doped N+ type SIC substrate 1 with a concentration of 1×10 15 cm -3 , the thickness is 10 microns, and the doping impurity is nitrogen (N);

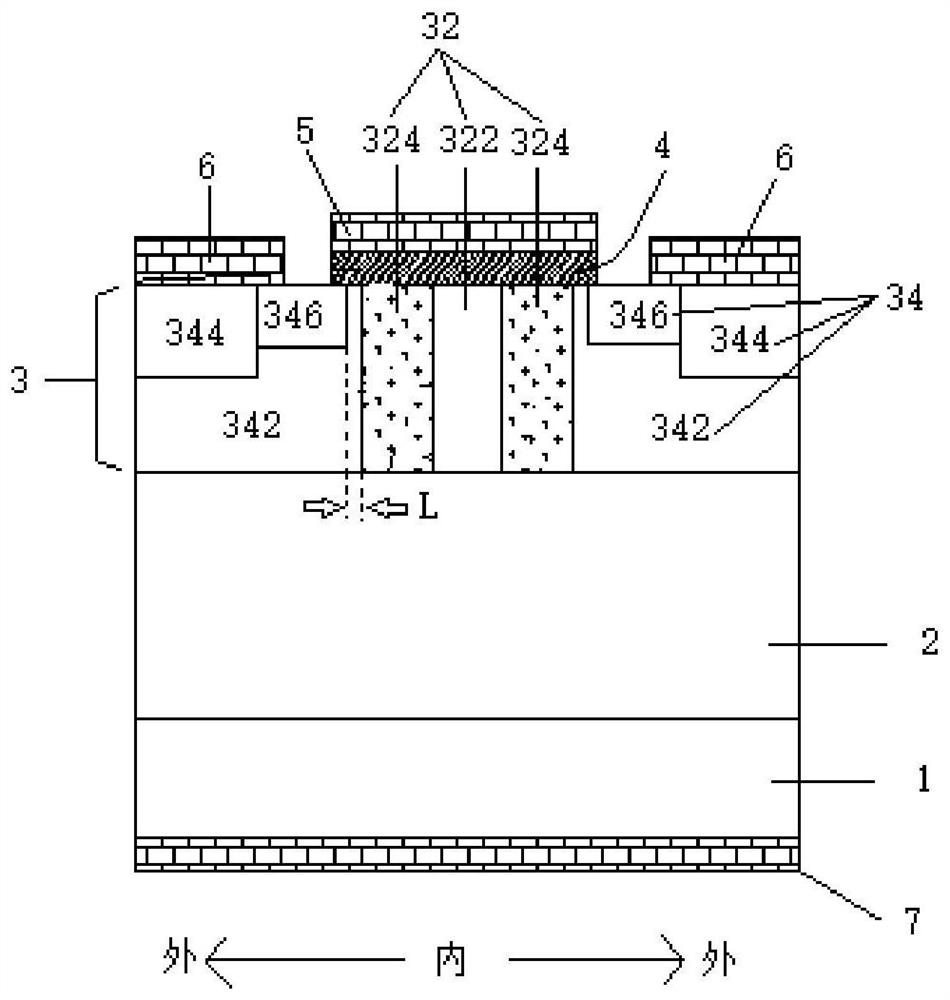

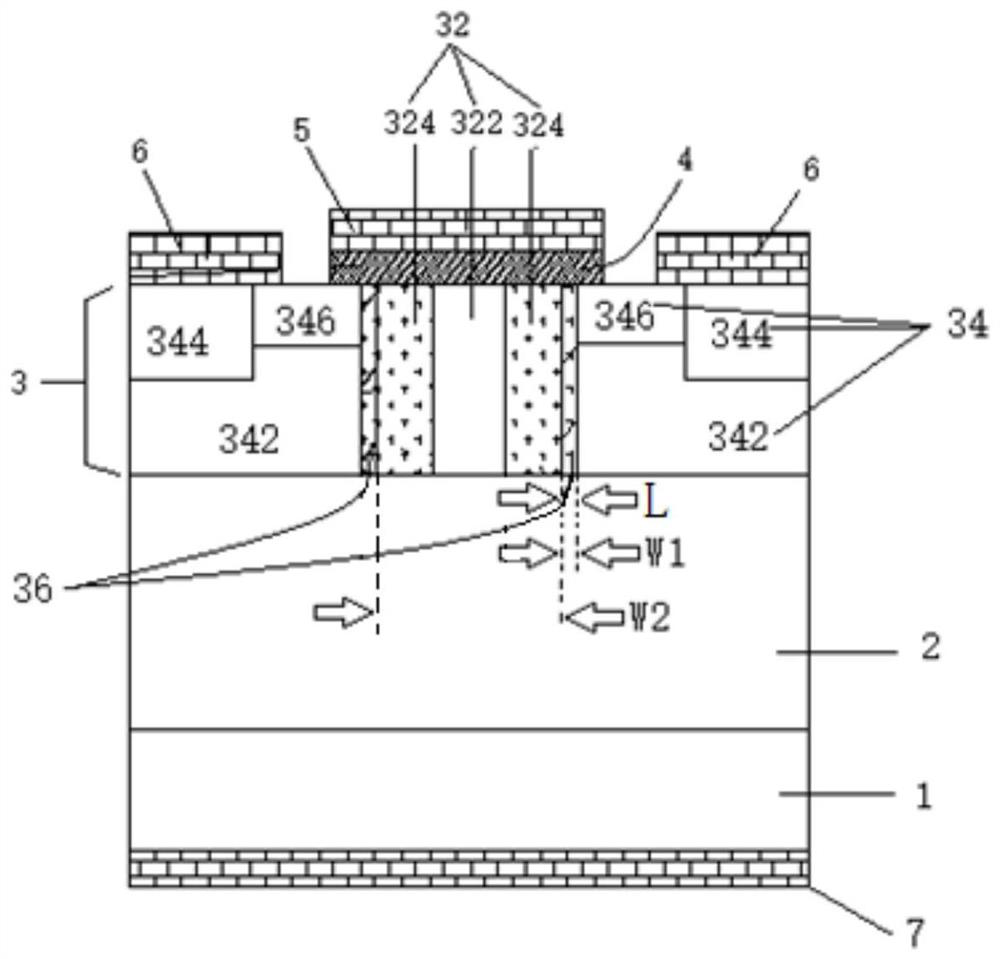

[0061] Step 2: Perform ion implantation on the N-type SIC doped layer 8 to form a P-well region and a P-doped region of a super junction structure, and the implantation concentration is 2×10 13 cm -3 , the doping impurity is aluminum (Al);

[0062] Step 3: Perform ion implantation on the N-type SIC doped layer 8 to form an N-doped region of a super junction structure, with an implantation concentration of 1.5×10 13 cm -3 ;

[0063] Step 4: Photolithography and implantation on the N-type SIC doped layer 8 to form a source region and a contact region; the doping concentration of the source region is 2×10 15 cm -3 , the doping concentration of the contact area is 1x10 16 cm -3 ; and carry out high temperature annealing after implantation, the annealing tempera...

Embodiment 2

[0068] Step 1: Epitaxially form an N-type SIC doped layer 8 on a heavily doped N+ type SIC substrate 1 with a concentration of 1×10 15 cm -3 , the thickness is 10 microns, and the doping impurity is nitrogen (N);

[0069] Step 2: Perform ion implantation on the N-type SIC doped layer 8 to form a P-well region and a P-doped region of a super junction structure, and the implantation concentration is 2×10 13 cm -3 , the doping impurity is aluminum (Al);

[0070] Step 3: Perform ion implantation on the N-type SIC doped layer 8 to form an N-doped region of a super junction structure, with an implantation concentration of 1.5×10 13 cm -3 ; The overlapping width with the P-well region is 0.5 microns respectively;

[0071] Step 4: Photolithography and implantation on the N-type SIC doped layer 8 to form a source region and a contact region; the doping concentration of the source region is 2×10 15 cm -3 , the doping concentration of the contact area is 1x10 16 cm -3 ; and perf...

PUM

| Property | Measurement | Unit |

|---|---|---|

| width | aaaaa | aaaaa |

| length | aaaaa | aaaaa |

| width | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com