Composite silicon substrate, preparation method and application thereof

A silicon substrate and silicon layer technology, applied in chemical instruments and methods, from chemical reactive gases, semiconductor/solid-state device manufacturing, etc., can solve the problems of increasing epitaxial thickness, high substrate price, substrate supply stability, and increasing final Problems such as device cost can be achieved by increasing the working voltage of the device, making the preparation method simple, and improving the quality of the crystal.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

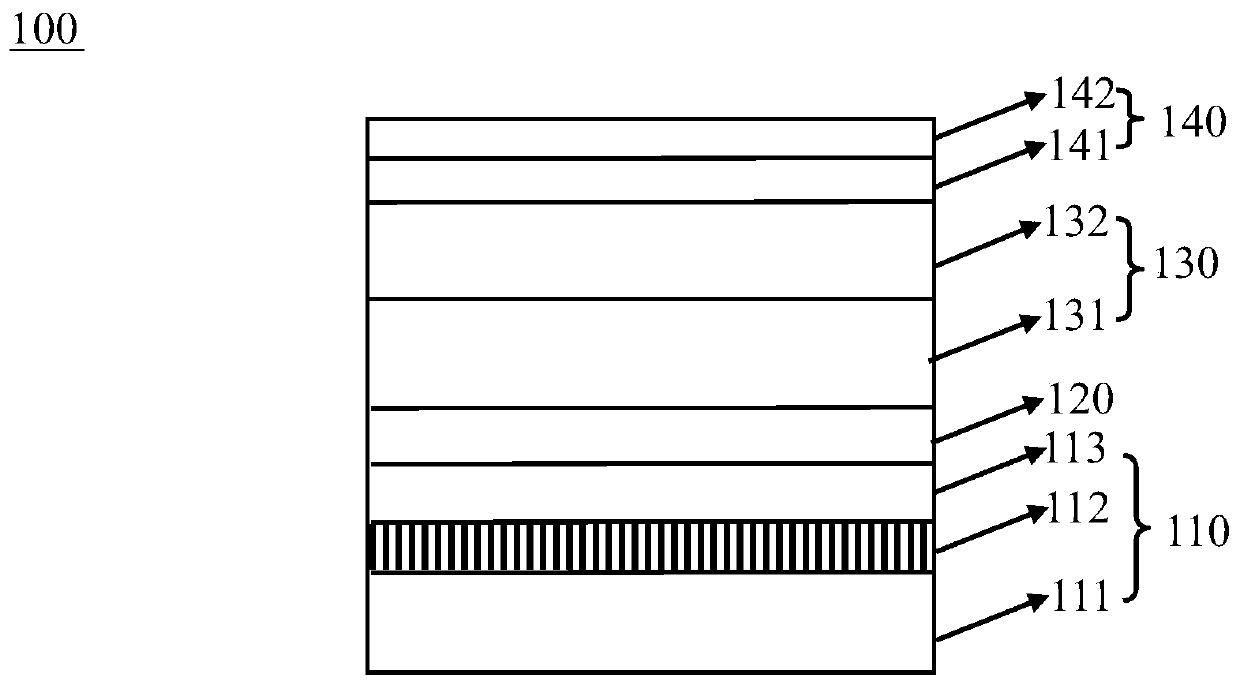

[0025] refer to figure 1 , a composite silicon substrate 110 includes a first silicon layer 111, a patterned silicon layer 112 and a second silicon layer 113, and the patterned silicon layer 112 is sandwiched between the first silicon layer 111 and the second silicon layer 113 An array of submicron pillars 1121 , the spacing of the submicron pillars forms a cavity 1122 .

[0026] The making of composite silicon substrate 110: throw a layer of about 1um thick photoresist AZ2460 on the front side of the silicon substrate of the (111) crystal plane, and then use the method of laser interference exposure to make a period (that is, adjacent sub-substrates) on the photoresist. Micron column interval) 500nm, photoresist point array pattern with a diameter of 200nm; then use the ICP etching method to transfer the submicron pattern of the photoresist to the silicon substrate; etch the depth on the silicon substrate by ICP The patterned silicon layer 112 of the array of 8um silicon sub...

Embodiment 2

[0029] The difference between embodiment 2 and embodiment 1 is that the second silicon layer is formed by bonding a thin silicon layer with a thickness of about 10 um (111) on the patterned silicon layer by using the Smart-cut method.

Embodiment 3

[0031] The difference between embodiment 3 and embodiment 1 is that the patterned silicon layer is porous silicon interposed between the first silicon layer and the second silicon layer, and the pores of the porous silicon form cavities.

[0032] Production method: Put the low-resistance silicon substrate as the anode into the mixed solution of hydrofluoric acid, deionized water and absolute ethanol, and metal platinum (Pt) as the cathode, and conduct electrochemical corrosion on the silicon substrate with an appropriate current A layer of porous silicon structure is formed on the surface of the substrate. By controlling the electrochemical corrosion conditions and the resistivity of the substrate, a porous silicon layer with a pore size of 100nm-1um can be prepared. The thickness of the porous silicon layer is about 10um, and the porosity (that is, the pores occupy The volume of the porous silicon layer) is between 20%-80%, more preferably 40%-60%, so as to ensure that the obt...

PUM

| Property | Measurement | Unit |

|---|---|---|

| pore size | aaaaa | aaaaa |

| size | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com