Mask plate, capacitor array, semiconductor device and preparation method thereof

A capacitor and mask technology, used in semiconductor devices, semiconductor/solid-state device components, electric solid-state devices, etc., can solve problems such as short circuits, DRAM reliability effects, unevenness, etc., and achieve simple process, improved accuracy, and cost. low effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

[0128] Please refer to image 3 , an embodiment of the present invention provides a method for preparing a capacitor array, comprising the following steps:

[0129] S1, providing a substrate, forming alternately stacked sacrificial layers and supporting layers on the substrate;

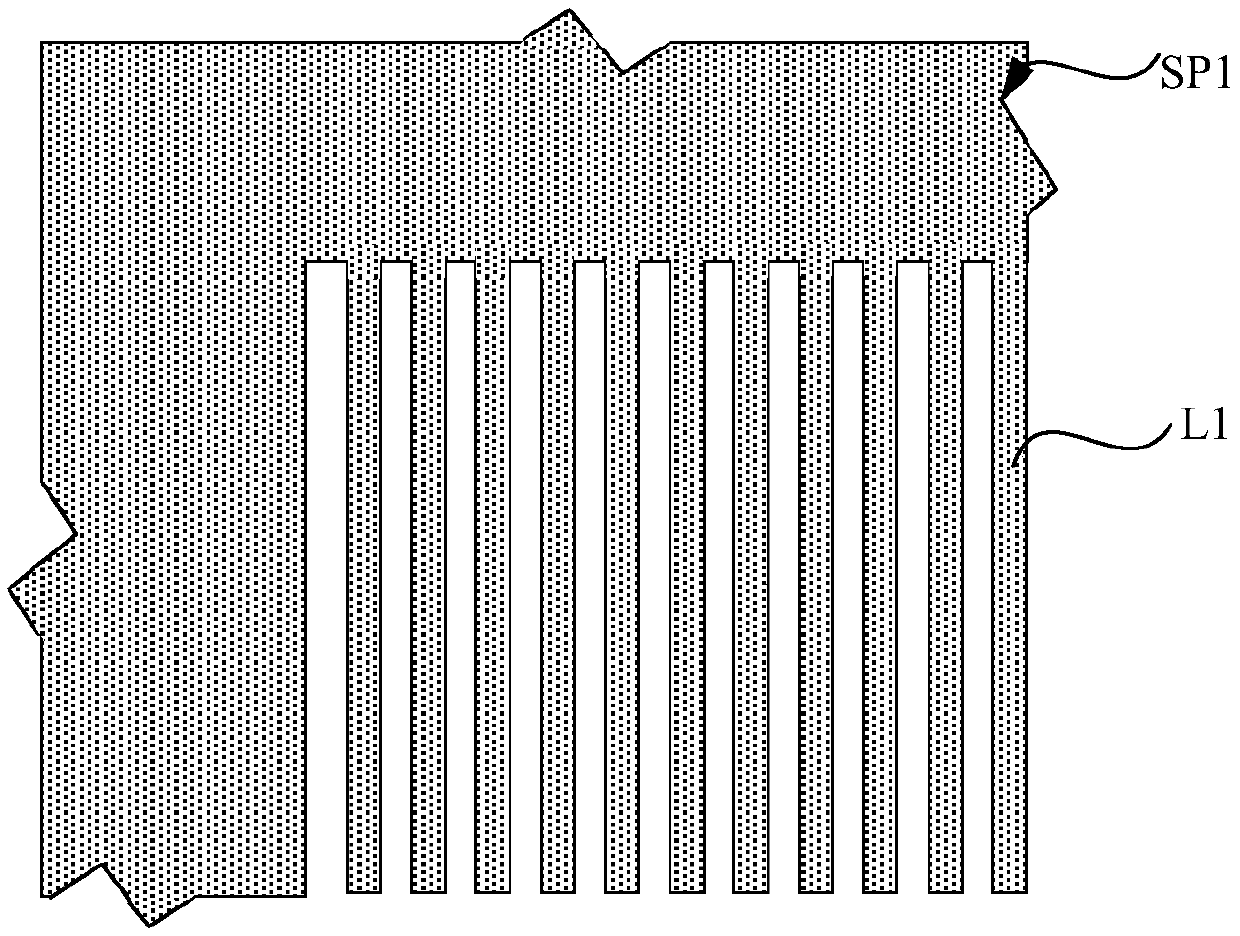

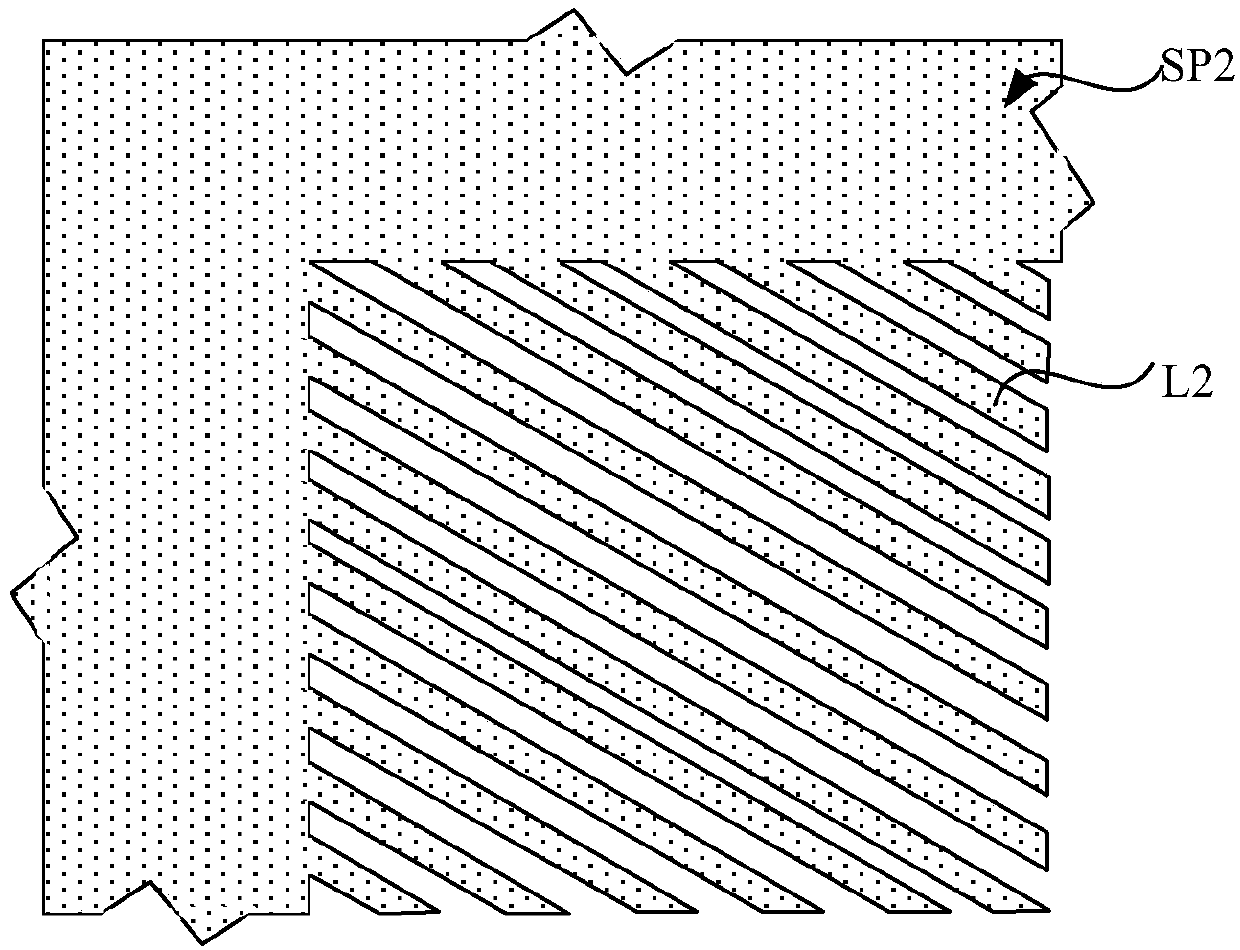

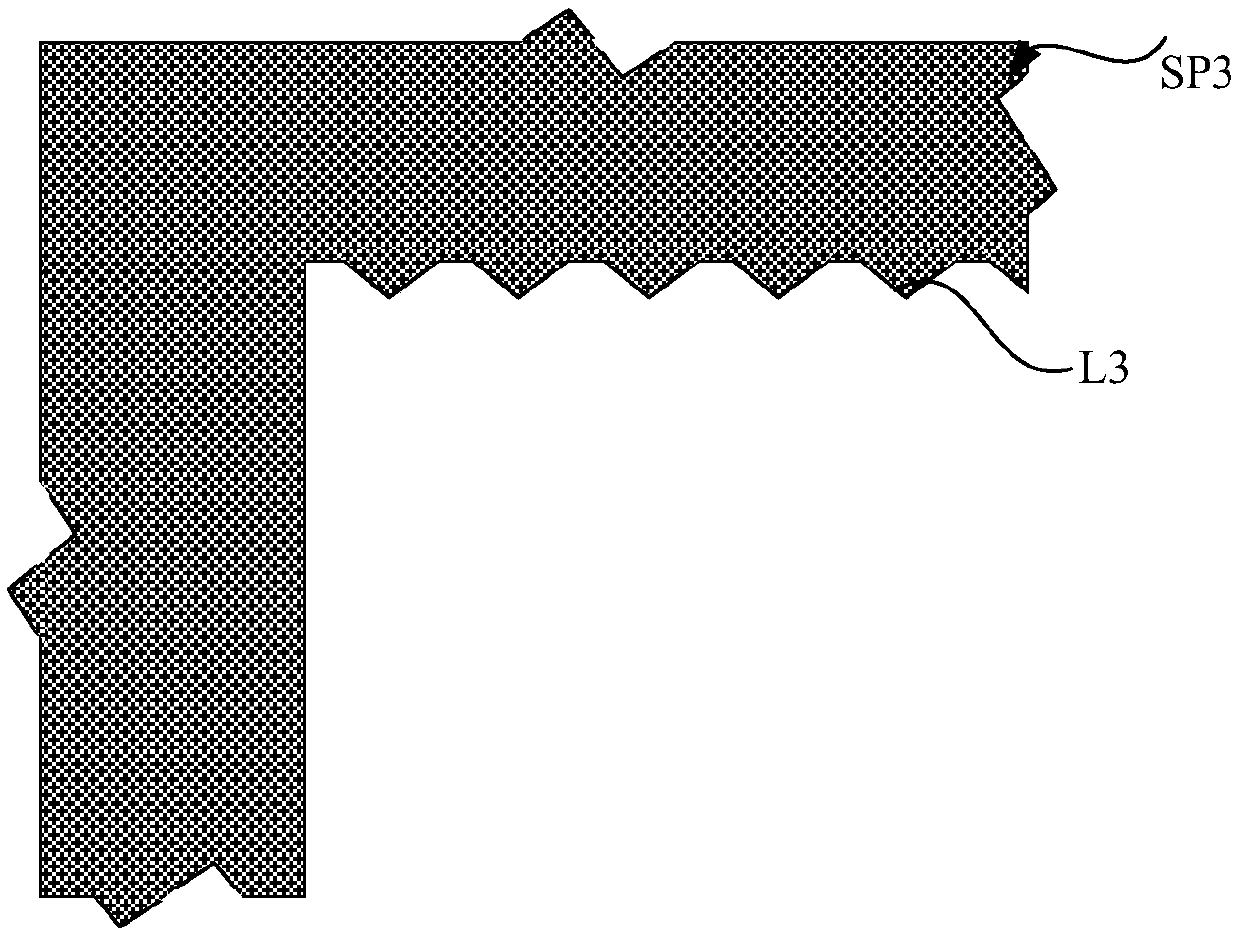

[0130] S2, using the mask plate of the present invention to form a patterned mask layer on the alternately stacked sacrificial layer and support layer through a single exposure process, the patterned mask layer includes a second grid pattern and surrounds A second ring pattern around the second grid pattern, the second grid pattern is interwoven with third lines extending along the first direction and fourth lines extending along the second direction, the second mesh Each second mesh in the grid pattern defines the location of a capacitor, the second annular pattern includes an annular opening immediately surrounding and surrounding the second mesh pattern and surrounding the annular opening away fro...

PUM

| Property | Measurement | Unit |

|---|---|---|

| angle | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com