Chip to be coated and processing process thereof

A processing process and chip technology, which is applied in the field of the chip to be laminated and its processing technology, can solve the problems of high edge chipping rate and high application failure rate, and achieve the effects of low edge chipping rate, low application failure rate and low production cost.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

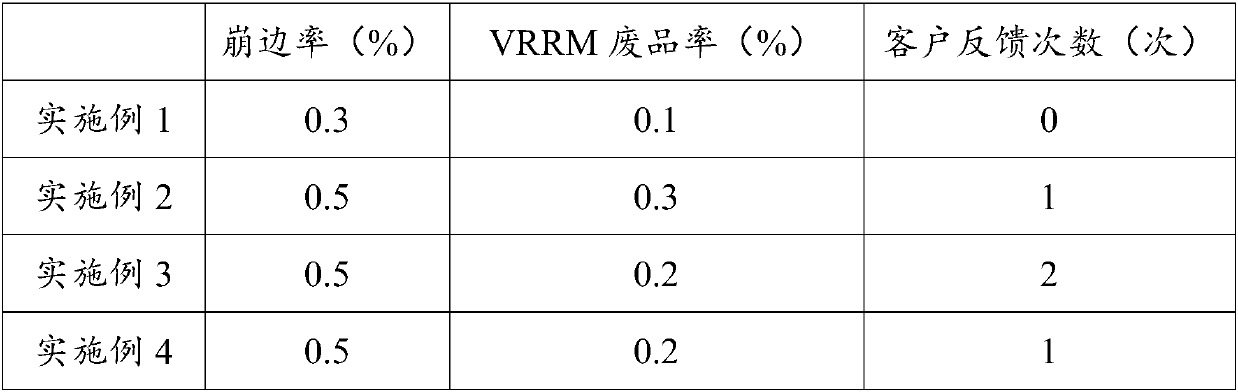

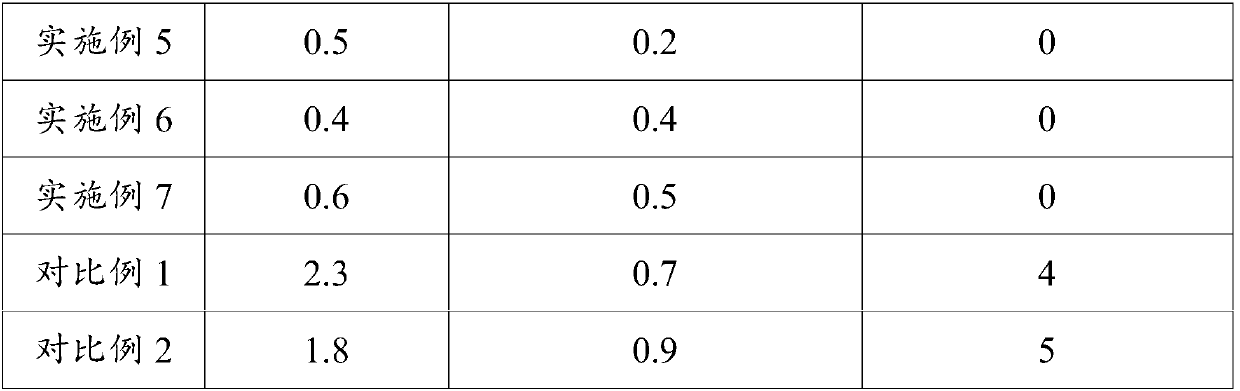

Examples

Embodiment 1

[0071] This embodiment provides a chip to be film-mounted, and its processing technology includes the following steps:

[0072] (a) first chip is carried out acid solution chemical corrosion, and wherein acid solution is the mixed solution of hydrofluoric acid solution and nitric acid solution, and the volume ratio of hydrofluoric acid solution (50wt%) and nitric acid solution (570wt%) is 1:5, Then select the chip after double-sided chemical etching to ensure that the etched lattice width is controlled at 300 μm and evenly distributed, and there are silicon oxide layers on the upper and lower surfaces of the chip;

[0073] (b) the lower surface of the chip is divided into a plurality of first sub-regions by photolithography, the first sub-regions include the first middle region and the first edge region, and the silicon oxide layer in the first middle region is removed, Then boron doping, aluminum doping and photolithography are performed on the first middle region to remove t...

Embodiment 2

[0076] This embodiment provides a chip to be film-mounted. The difference between the processing technology of this embodiment and Embodiment 1 is that the etching lattice width is 100 μm.

Embodiment 3

[0078] This embodiment provides a chip to be film-mounted. The difference between the processing technology of this embodiment and Embodiment 1 is that the etching lattice width is 500 μm.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com