Nano-porous LED array chip with anti-reflection passivation layer and preparation method thereof

A technology of LED arrays and nanoholes, applied in electrical components, electrical solid devices, circuits, etc., can solve the disadvantages of high signal-to-noise ratio and high-speed visible light communication, large difference in refractive index between GaN material and air, and large thickness of electron injection layer and other issues, to achieve high yield, meet the isolation effect, and reduce the effect of leakage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

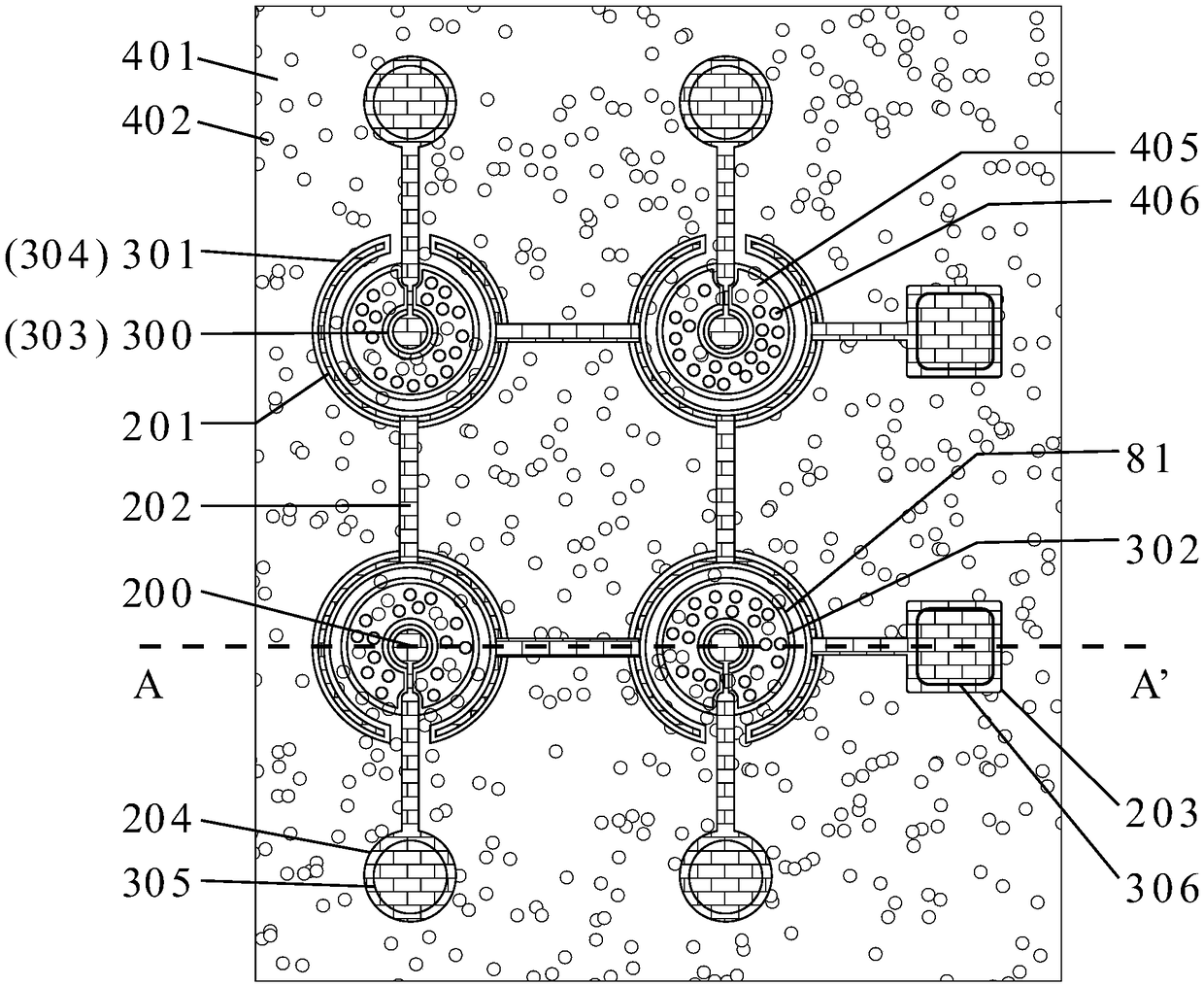

[0049] Embodiment 1, the preparation steps of the nanohole LED array chip with an anti-reflection passivation layer are as follows.

[0050] (1) GaN-based LED epitaxial wafers are prepared by metal oxide vapor deposition. The structure of GaN-based LED epitaxial wafers includes sapphire substrate 1, GaN buffer layer 2, unintentionally doped GaN layer 3, and N-type doped GaN layer. 4. Quantum well layer 5 , P-type doped AlGaN layer 6 and P-type doped GaN layer 7 . Such as Figure 3a shown.

[0051] (2) Deposit a transparent current spreading layer ITO 8 with a thickness of 100 nm on the GaN-based LED epitaxial wafer using electron beam evaporation, in N 2 200sccm, O 2 Rapid annealing in a mixed atmosphere of 35 sccm for 3 minutes to form an ohmic contact, and then use ultraviolet lithography and wet etching, and soak in ITO etching solution for 15 minutes at room temperature to form an ITO disk distributed only in the active area of the light-emitting unit. The diameter ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Diameter | aaaaa | aaaaa |

| Depth | aaaaa | aaaaa |

| Width | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com