Superjunction device and method of manufacturing the same

A technology of super junction devices and manufacturing methods, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., capable of solving problems such as threshold voltage exceeding specifications

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

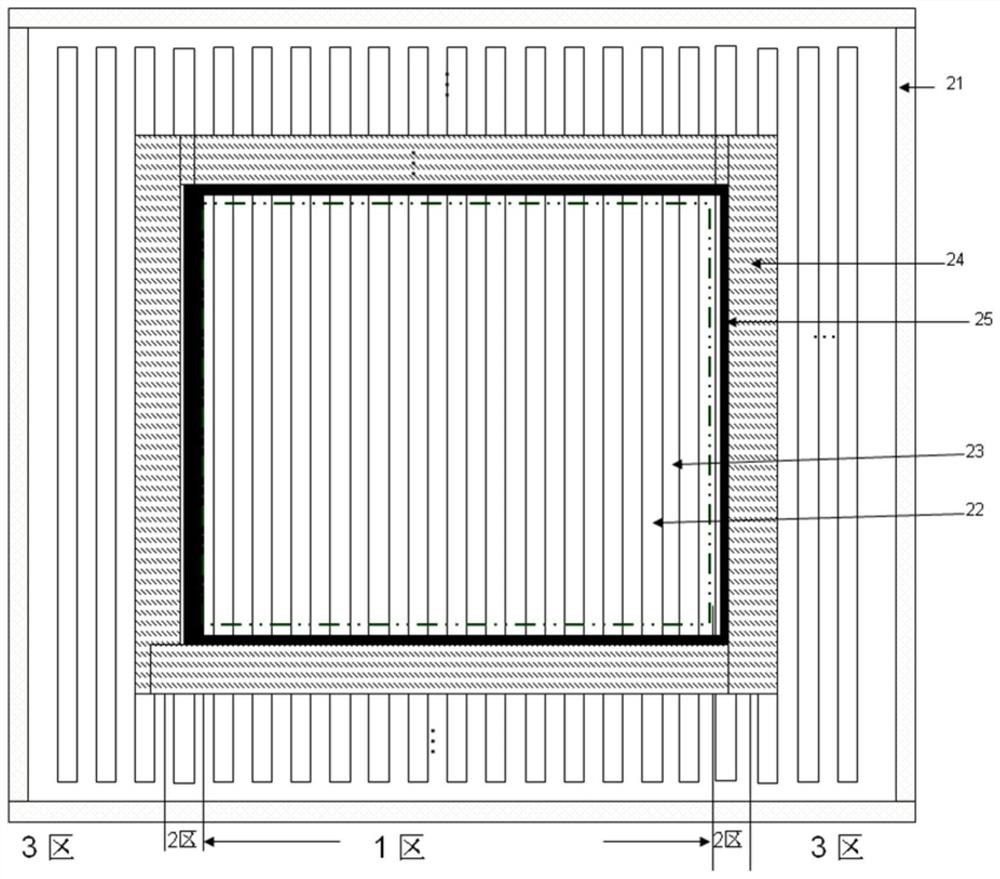

[0072] like figure 1 As shown, it is a top view of an existing superjunction device; a general superjunction device structure includes a charge flow region, a terminal region laterally subjected to a reverse bias voltage, and a transition region between the charge flow region and the terminal region, and the terminal region around the periphery of the charge flow region, figure 1 Zone 1 represents the charge flow region, Zone 2 represents the transition region, and Zone 3 represents the terminal region.

[0073] Zone 1 includes a super junction structure composed of alternately arranged P-type pillars 22 and N-type pillars 23, figure 1 Both the P-type pillars 22 and the N-type pillars 23 are strip-shaped. The N-type pillar 23 provides a conduction path when the super-junction device is turned on, and the P-type pillar 22 and the N-type pillar 23 deplete each other and bear the reverse bias together when the super-junction device is reverse-biased.

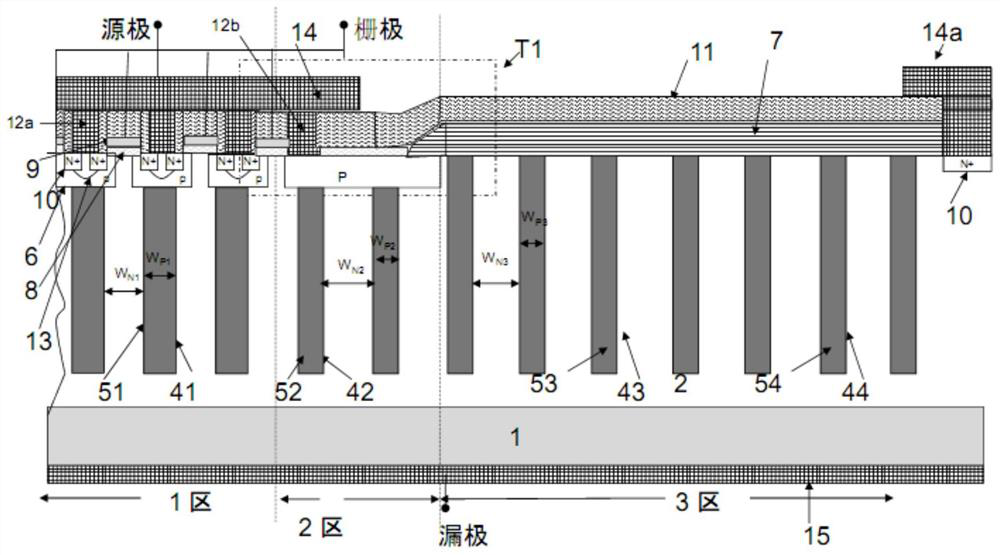

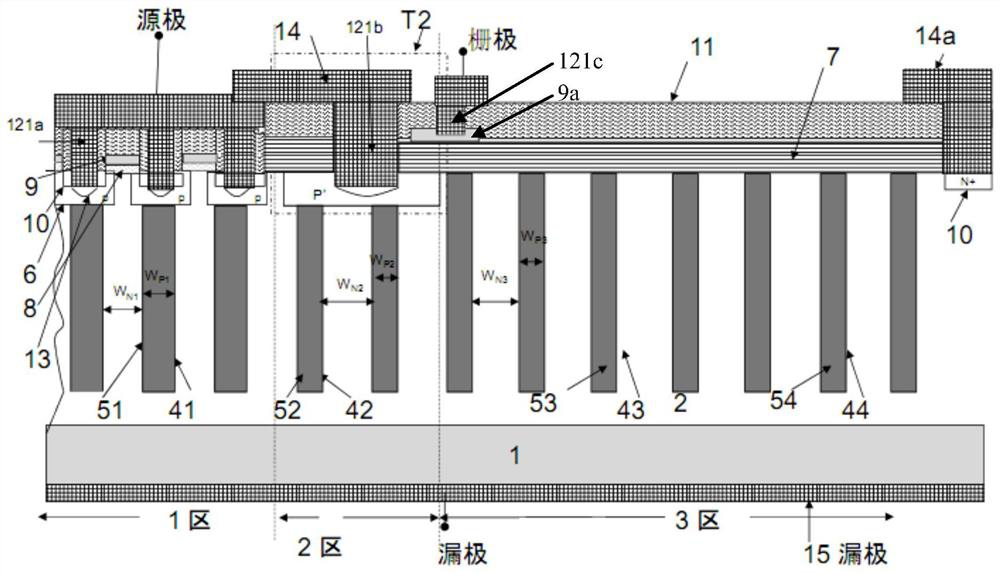

[0074] Region 2 and Regi...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com