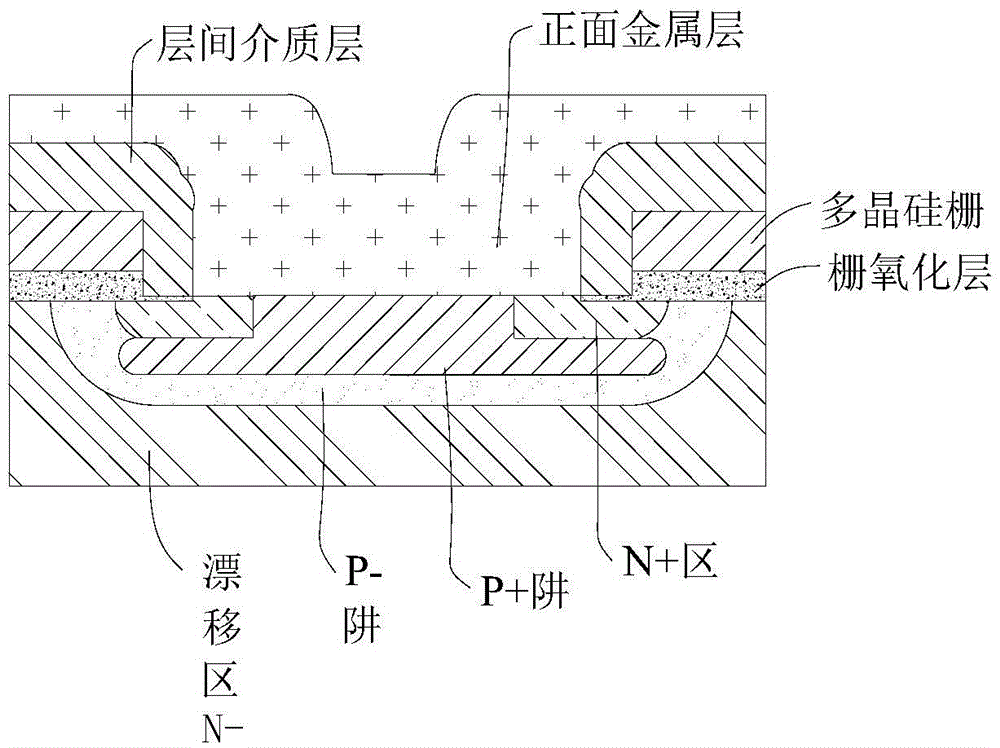

Power semiconductor device and preparation method thereof

A technology of power semiconductors and devices, which is applied in the field of power semiconductor devices and their preparation, and can solve problems such as increasing the difficulty of process control, the preparation process of power semiconductor devices needs to be improved, and large parameter fluctuations.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] Embodiments of the present invention are described in detail below. The embodiments described below are exemplary only for explaining the present invention and should not be construed as limiting the present invention. If no specific technique or condition is indicated in the examples, it shall be carried out according to the technique or condition described in the literature in this field or according to the product specification. The reagents or instruments used were not indicated by the manufacturer, and they were all commercially available conventional products.

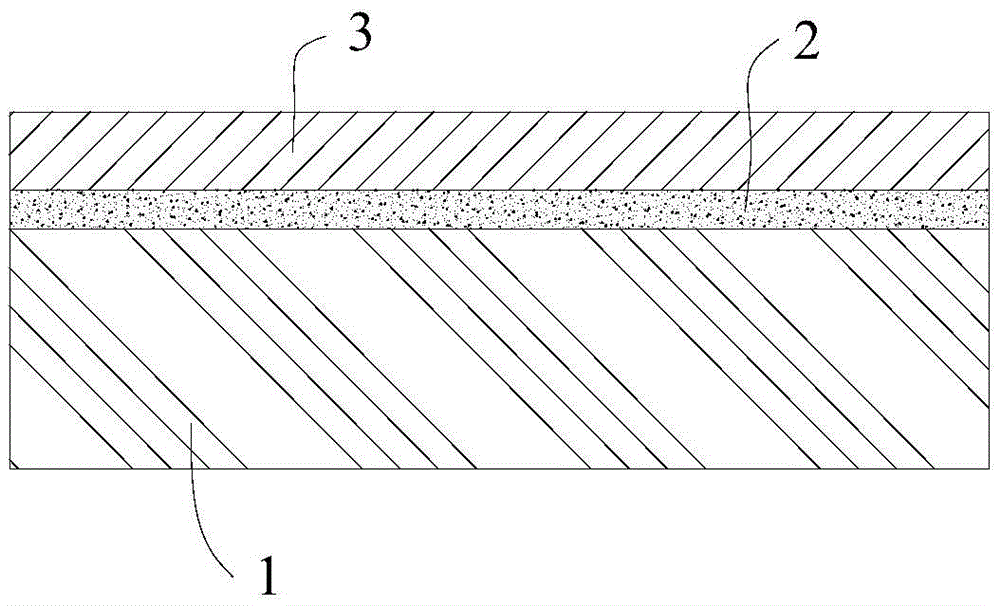

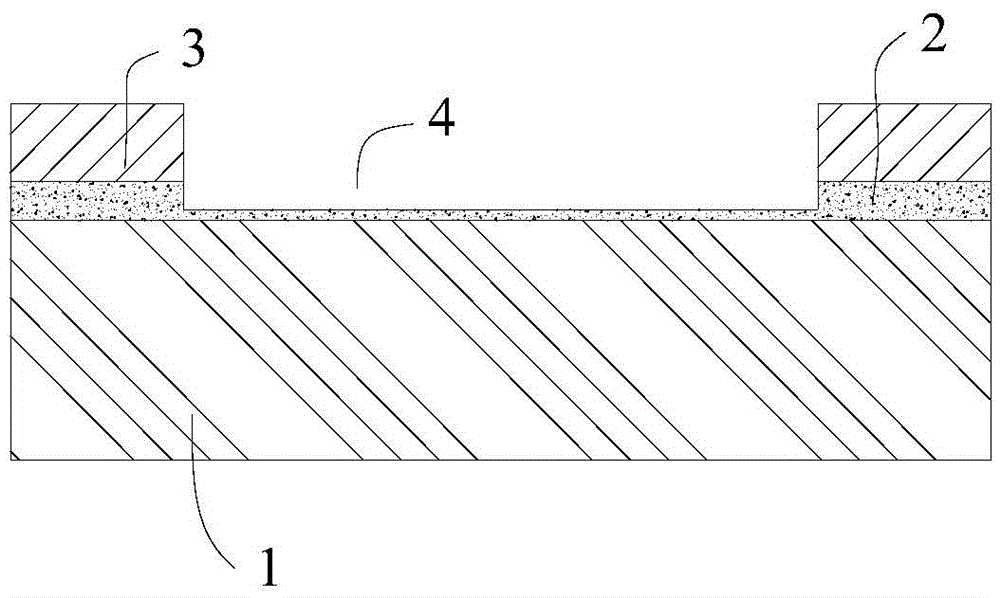

[0027] In one aspect of the invention, the invention provides a method of making a power semiconductor device. According to an embodiment of the present invention, refer to Figure 2A-Figure 2O , the method includes the following steps:

[0028] (1) Refer to Figure 2A , forming a gate oxide layer 2 on the upper surface of the substrate 1 , and depositing a polysilicon gate 3 on the upper surface of th...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| height | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com