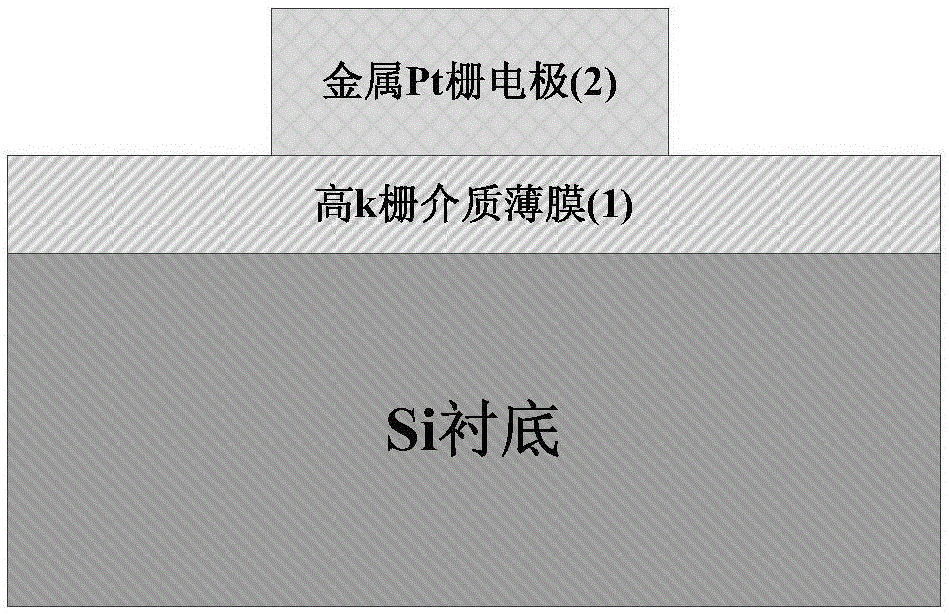

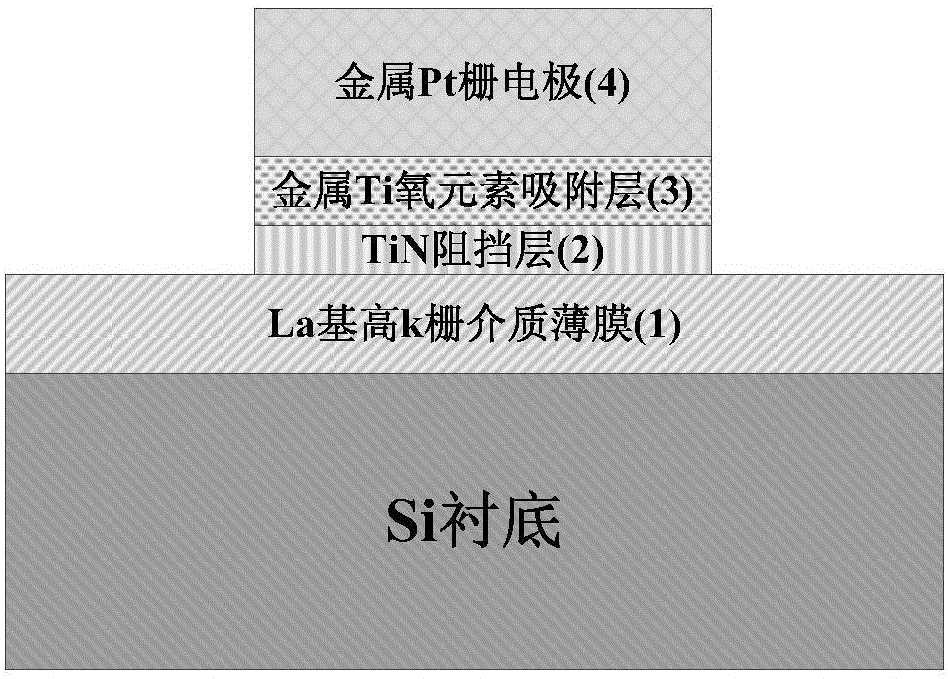

La-based medium material high-K metal gate structure based on Si substrate and preparation method thereof

A dielectric material and metal gate technology, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problem of affecting the overall quality of the high-K metal gate structure, increasing the thickness of the equivalent oxide layer, and deteriorating the interface characteristics of the device, etc. problems, to achieve good conductivity, reduce power consumption, and increase the dielectric constant.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

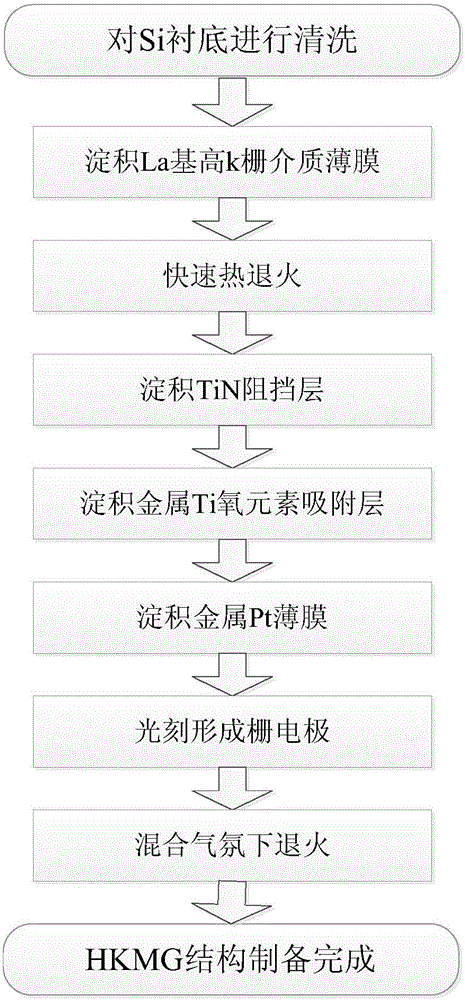

[0031] Embodiment 1: prepare La 2 o 3 High-k metal gate structure of high-k gate dielectric material.

[0032] Step 1, cleaning the silicon wafer.

[0033] 1a. Use NH in a ratio of 5:1:1 4 OH, H 2 o 2 and H 2 O equip SC-1 solution with HF and H at a ratio of 1:50 2 O equipped with HF solution;

[0034] 1b. Put the Si wafer in the SC-1 solution at a temperature of 75 ° C for 10 minutes, and rinse it with deionized water for 2 minutes to remove organic pollutants or attached particles on the Si wafer;

[0035] 1c. Place the Si wafer cleaned in the SC-1 solution in the HF solution for a second cleaning for 60 seconds, and rinse it with deionized water to remove the natural oxide layer SiO on the surface of the Si wafer 2 ;

[0036] 1d. Place the Si wafer after the second cleaning in deionized water and ultrasonically clean it for 5 minutes to remove the adsorbed particles on the surface, then rinse it with deionized water for 2 minutes, and dry it with 99.999% high-purity ...

Embodiment 2

[0063] Embodiment 2, preparation La 2 o 3 / Al 2 o 3 The stacked structure serves as a high-k metal gate structure with a high-k gate oxide layer.

[0064] Step 1, cleaning the silicon wafer.

[0065] The specific implementation of this step is the same as step 1 of Embodiment 1.

[0066] Step 2, put the cleaned Si wafer into the reaction chamber of the atomic layer deposition equipment, and use the atomic layer deposition method to deposit La on the dried Si wafer. 2 o 3 / Al 2 o 3 laminated film.

[0067] refer to Figure 4 and Figure 5 , the specific implementation of this step is as follows:

[0068] 2.1) In the ultra-clean room environment, put the pretreated and cleaned Si wafer into the reaction chamber of the atomic layer deposition equipment, then evacuate the chamber pressure to 15hPa, heat the temperature to 300°C, set the The 99.999% high-purity nitrogen flow used for washing is 120 sccm, and the deposition La 2 o 3 The number of cycles m and the depos...

Embodiment 3

[0097] Embodiment 3, preparation LaAlO 3 High-K metal gate structure of high-k gate oxide material.

[0098] Step A, cleaning the silicon wafer.

[0099] The specific implementation of this step is the same as step 1 of Embodiment 1.

[0100] Step B, put the cleaned Si wafer into the reaction chamber of the atomic layer deposition equipment, and use the atomic layer deposition method to deposit LaAlO on the dried Si wafer 3 film.

[0101] refer to Figure 6 , the specific implementation of this step is as follows:

[0102] B1. In the ultra-clean room environment, put the pretreated and cleaned Si wafer into the reaction chamber of the atomic layer deposition equipment, then evacuate the pressure of the chamber to 20hPa, heat the temperature to 310°C, and set the blower to The 99.999% high-purity nitrogen gas flow used for washing is 150 sccm, and the deposition La 2 o 3 The number of cycles m = 1, the deposition of Al 2 o 3 The number of cycles n=1;

[0103] B2. Depo...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com