Ring-gate structure field effect transistor and preparation method thereof

A technology of structure field and transistor, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as the influence of semiconductor working performance, and achieve the effect of size reduction and good insulation properties

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

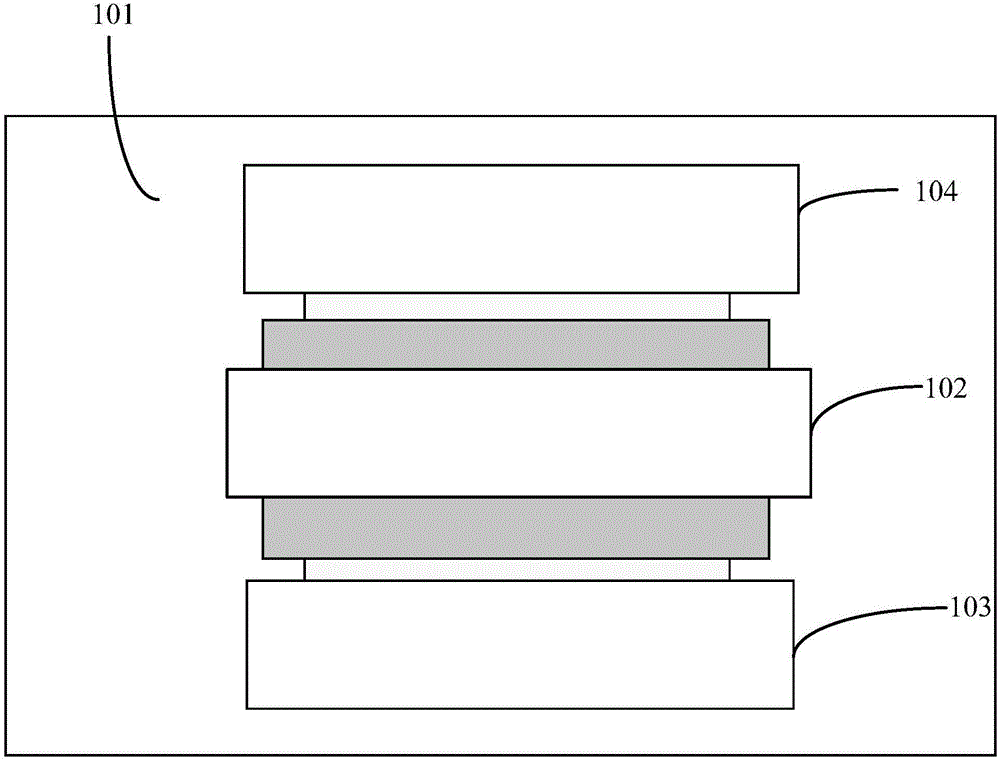

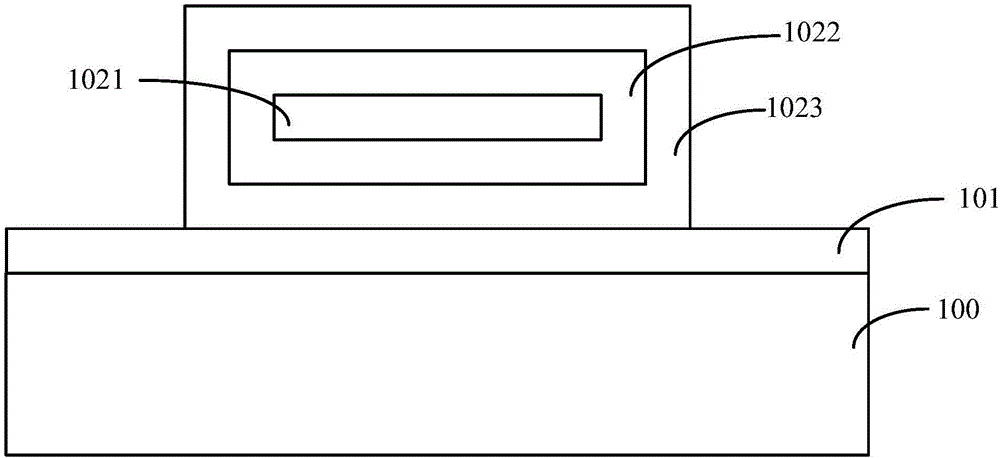

Image

Examples

preparation example Construction

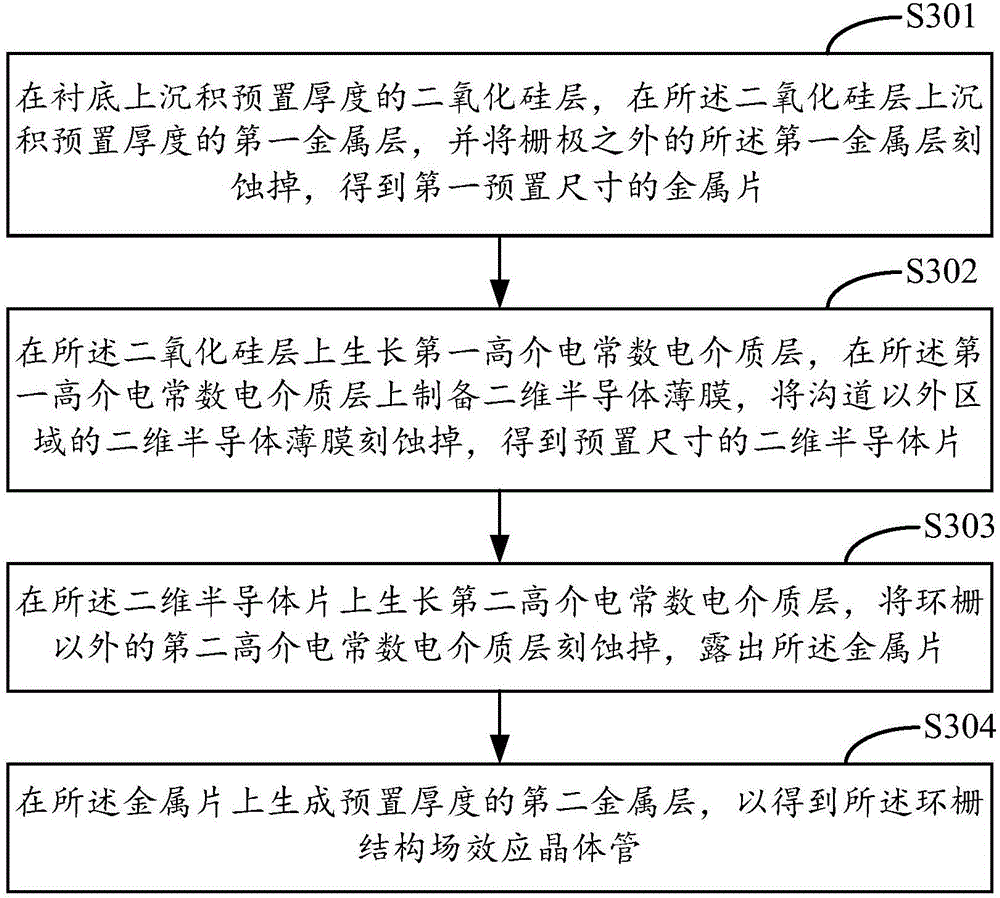

[0034] The present invention also provides image 3 A method for preparing a field effect transistor with a gate-all-around structure shown, comprising:

[0035] S301, depositing a silicon dioxide layer with a preset thickness on the substrate, depositing a first metal layer with a preset thickness on the silicon dioxide layer, and etching away the first metal layer except the gate , to obtain a metal sheet of the first preset size;

[0036] S302, growing a first high-permittivity dielectric layer on the silicon dioxide layer, preparing a two-dimensional semiconductor film on the first high-permittivity dielectric layer, and etching the two-dimensional semiconductor film in areas other than the channel Get a two-dimensional semiconductor chip with a preset size;

[0037] S303, growing a second high-permittivity dielectric layer on the two-dimensional semiconductor sheet, and etching away the second high-permittivity dielectric layer except the ring gate, exposing the metal s...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com