A Scheduling Method of Hardware Accelerator in C-ran

A technology of hardware accelerator and scheduling method, which is applied in the direction of instruments, electrical components, multi-programming devices, etc., can solve the problems of high computational complexity, consumption of signal processing time, and CPU processing resources occupied by computationally intensive modules, and achieve system throughput The effect of high rate, increased system throughput, and improved signal processing speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0034] The present invention will be described in detail below with reference to the accompanying drawings and specific embodiments. This embodiment is carried out on the premise of the technical solution of the present invention, and detailed implementation and specific operation process are given, but the protection scope of the present invention is not limited to the following embodiments.

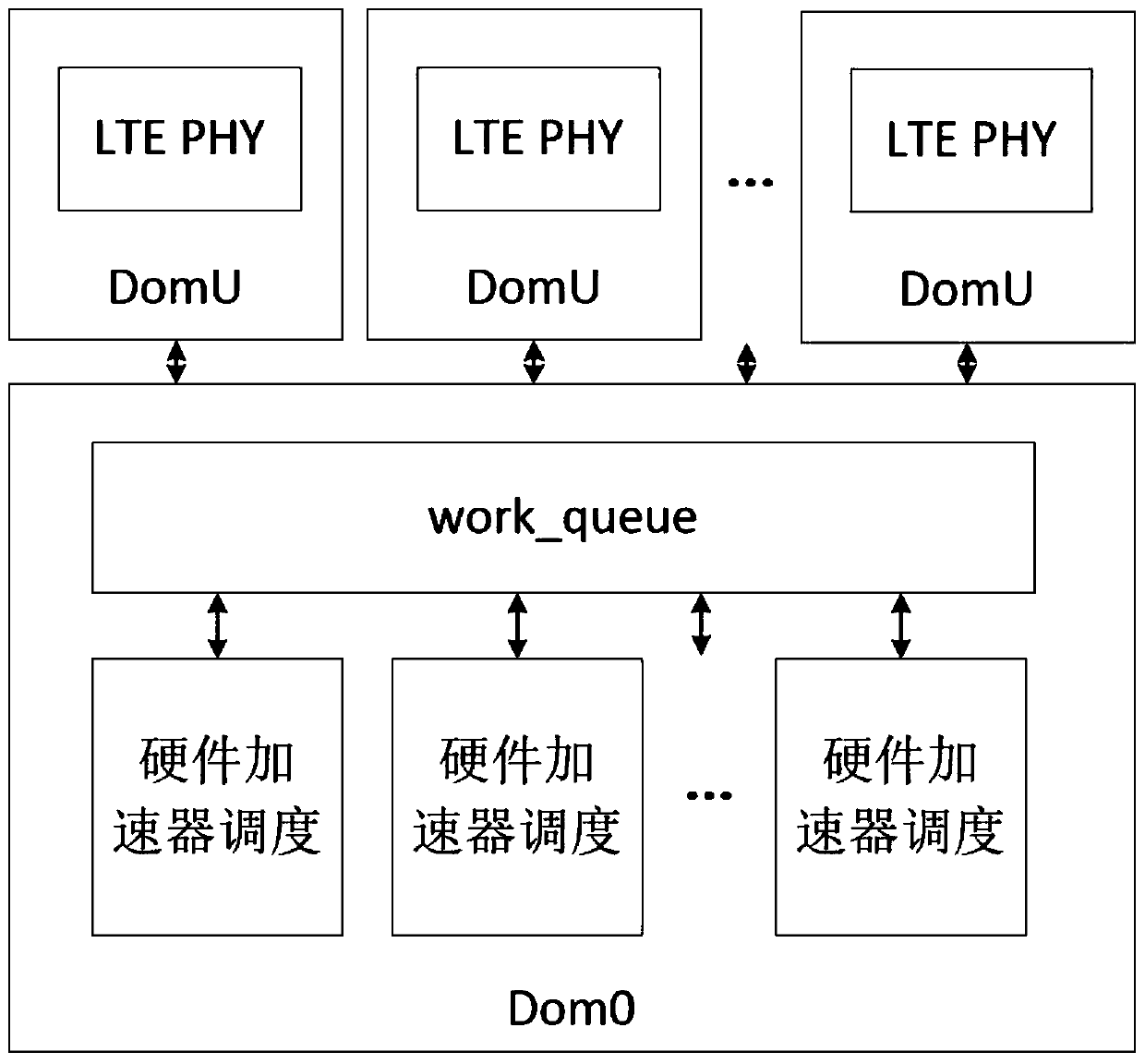

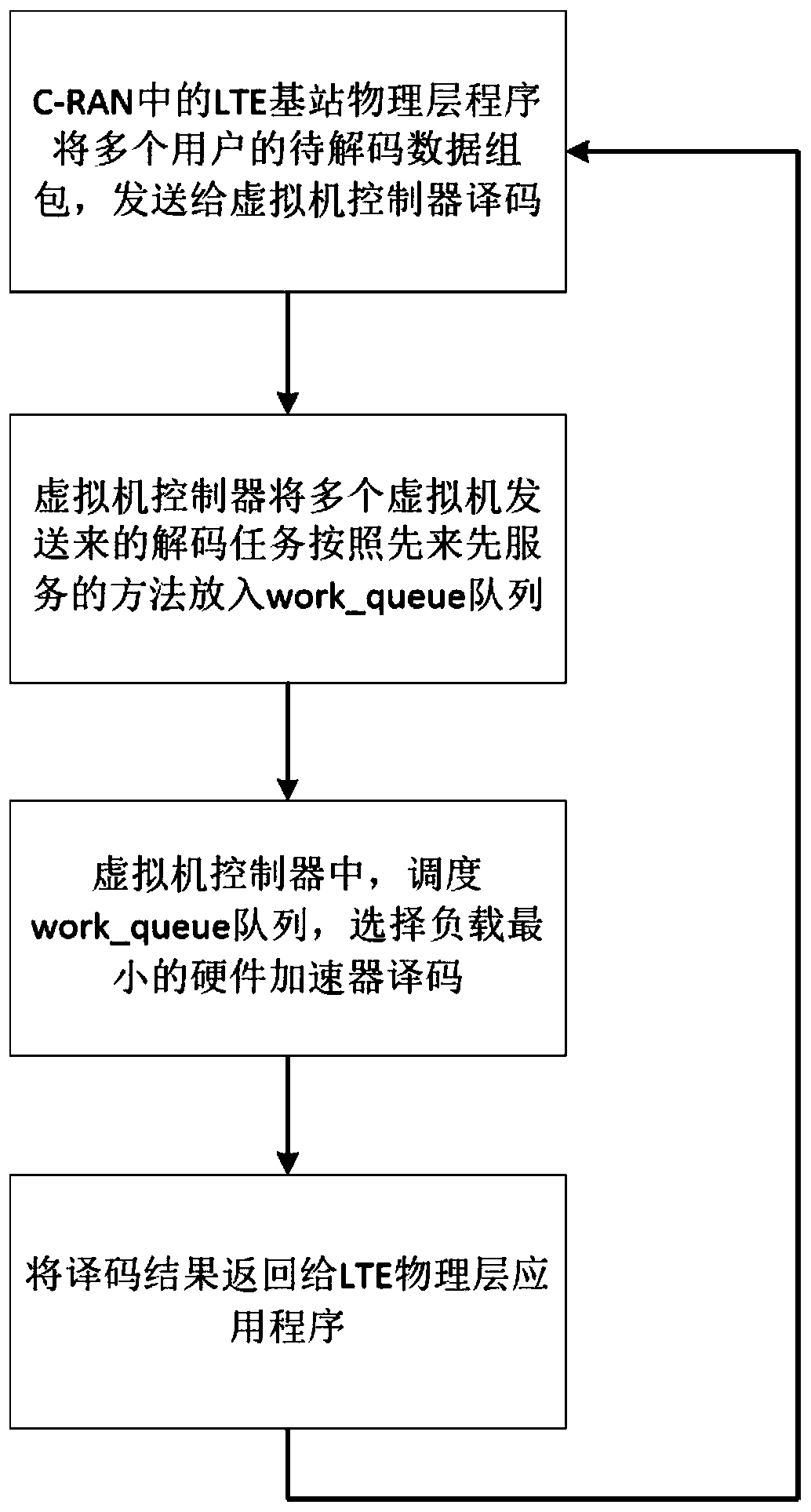

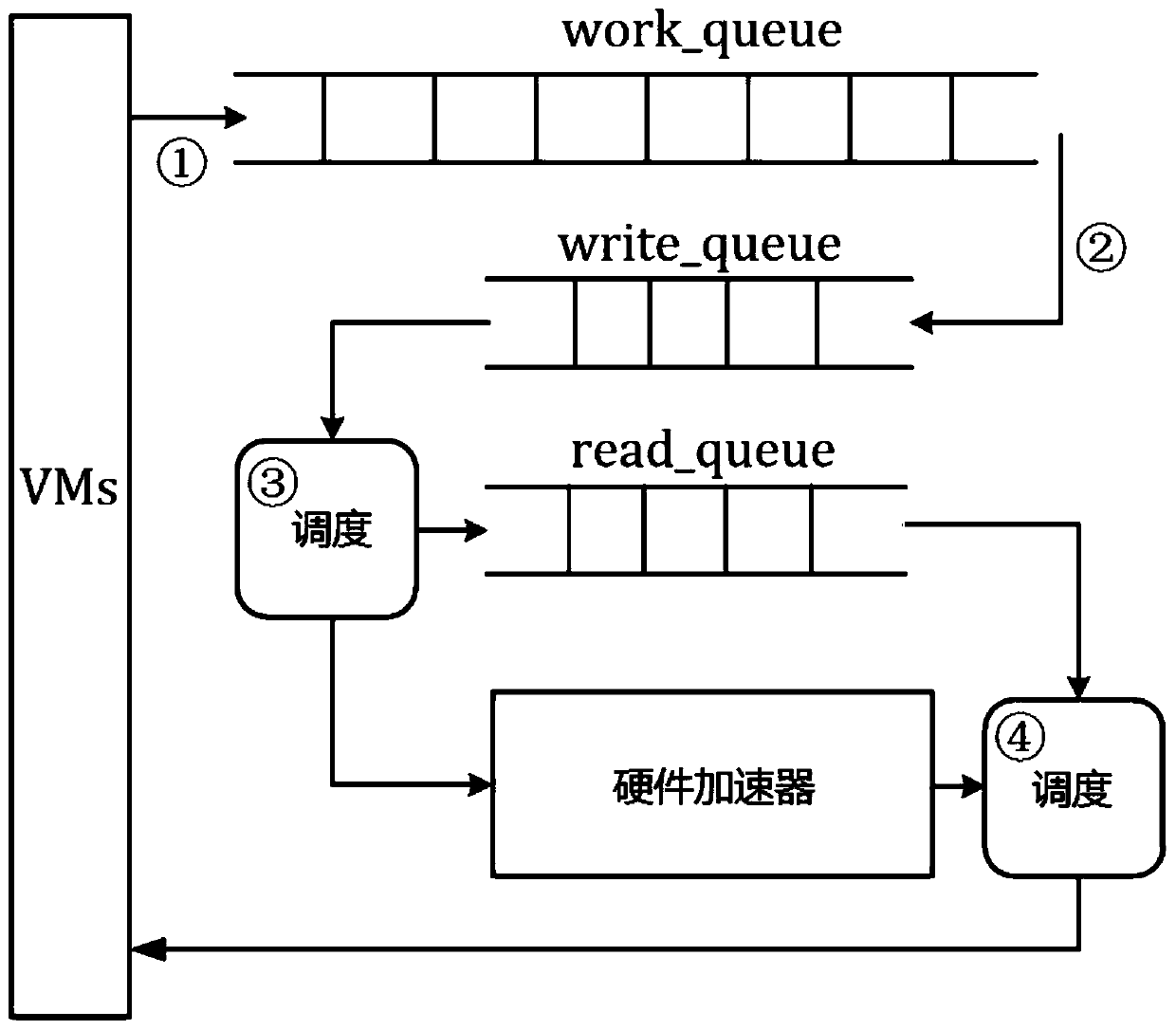

[0035] The system overall structure of the dispatching method of hardware accelerator in a kind of C-RAN is as follows figure 1 shown:

[0036] Run the LTE base station physical layer program (LET PHY) in the virtual machine; the modules with high computational complexity are implemented with hardware accelerators, and multiple hardware accelerator devices are connected to the server through PCIe (PCI-Express is the latest bus and interface standard) The host installs the device driver, and the server calls the device driver to communicate with the device;

[0037] Install Xen, modify...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com