Semiconductor device manufacturing method, semiconductor device and electronic device

A manufacturing method, semiconductor technology, applied in the direction of semiconductor devices, semiconductor/solid device manufacturing, semiconductor/solid device components, etc., can solve the impact of electrical conductivity, affect aluminum pads and the first metal layer, large expansion, etc. problems, to avoid oxidation, reduce thermal mismatch, and reduce internal stress

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

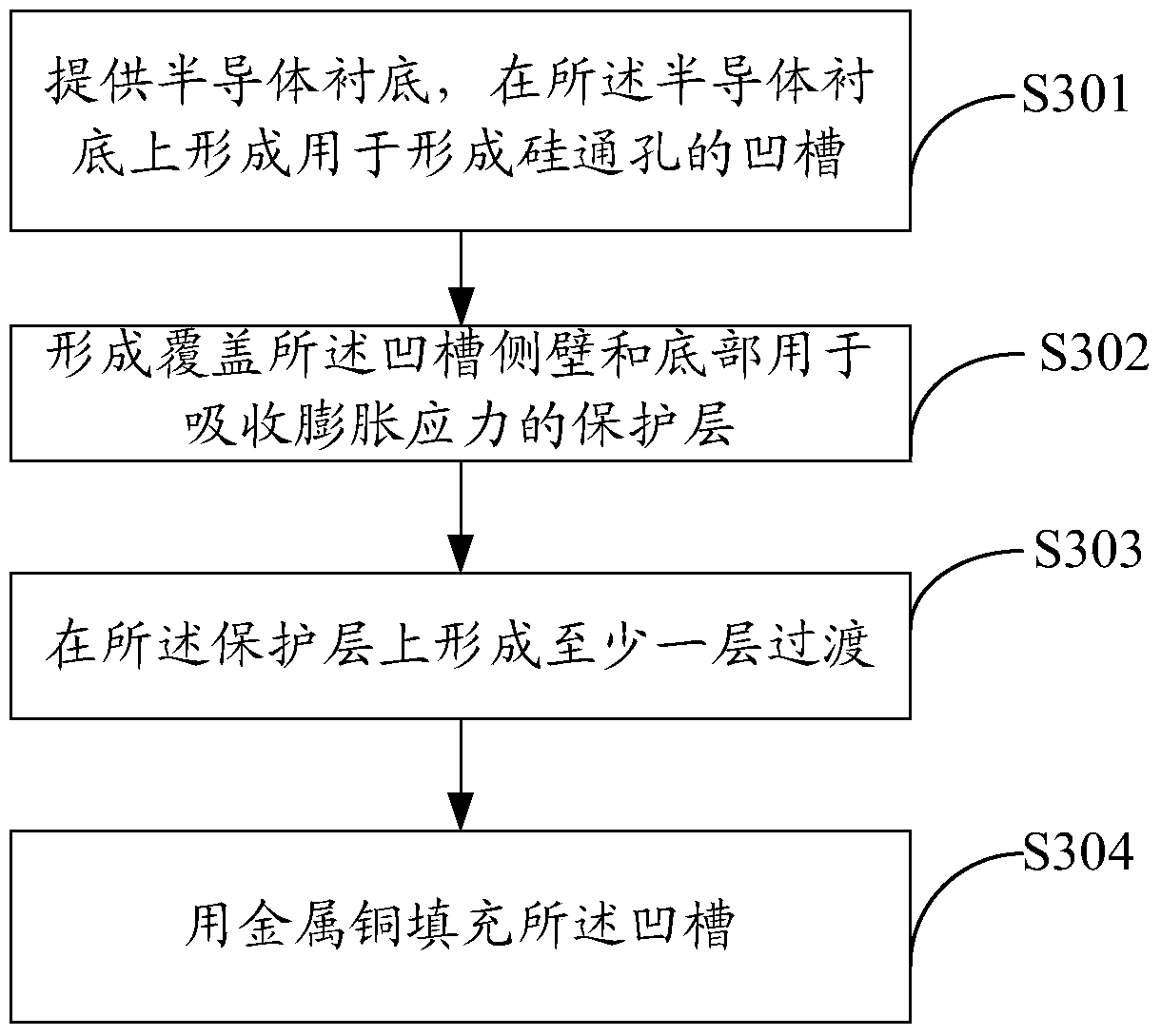

[0045] Combine below Figure 4A ~ Figure 4F The manufacturing method of the semiconductor device of the present invention is described in detail.

[0046] First, if Figure 4A As shown, a semiconductor substrate 400 is provided, and a groove 401 for forming a through silicon via is formed on the semiconductor substrate 400 . The semiconductor substrate 400 may be at least one of the materials mentioned below: silicon, germanium. In addition, other devices, such as PMOS and NMOS transistors, may be formed on the semiconductor substrate. An isolation structure may be formed in the semiconductor substrate, and the isolation structure is a shallow trench isolation (STI) structure or a local oxide of silicon (LOCOS) isolation structure. CMOS devices may also be formed in the semiconductor substrate, such as transistors (eg, NMOS and / or PMOS) and the like. Similarly, a conductive member may also be formed in the semiconductor substrate, and the conductive member may be the gate,...

Embodiment 2

[0066] The present invention also provides a semiconductor device fabricated by the method described in Embodiment 1, a semiconductor substrate 500, a groove 501 formed on the semiconductor substrate 500 for forming through-silicon vias, and a groove 501 formed in the groove A protective layer 502 for absorbing expansion stress, at least one transition layer and a metal copper layer 506 are sequentially formed in 501, wherein the transition layer is made of a metal material, and the thermal expansion coefficient of the transition layer is smaller than that of copper.

[0067] Preferably, the transition layer is multi-layered, and the thermal expansion coefficient of each transition layer increases gradually along the direction away from the protective layer.

[0068] As an example, in this embodiment, the transition layer includes a first transition layer 503 , a second transition layer 504 and a third transition layer 505 sequentially formed on the protective layer 502 , and t...

Embodiment 3

[0073] The present invention further provides an electronic device including the aforementioned semiconductor device.

[0074] The electronic device can be any electronic product or equipment such as mobile phone, tablet computer, notebook computer, netbook, game console, TV, VCD, DVD, navigator, camera, video recorder, voice recorder, MP3, MP4, PSP, etc. It is an intermediate product with the above-mentioned semiconductor device, for example: a mobile phone motherboard with the integrated circuit, etc. In this implementation, take PDA as an example, such as Image 6 shown.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com