Field-effect transistor and its manufacturing method

A field-effect transistor and semiconductor technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of affecting the performance of nano-scale devices, easy generation of epitaxial layers, and large contact resistance, etc., to reduce contact resistance, The effect of improving performance, improving quality and speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

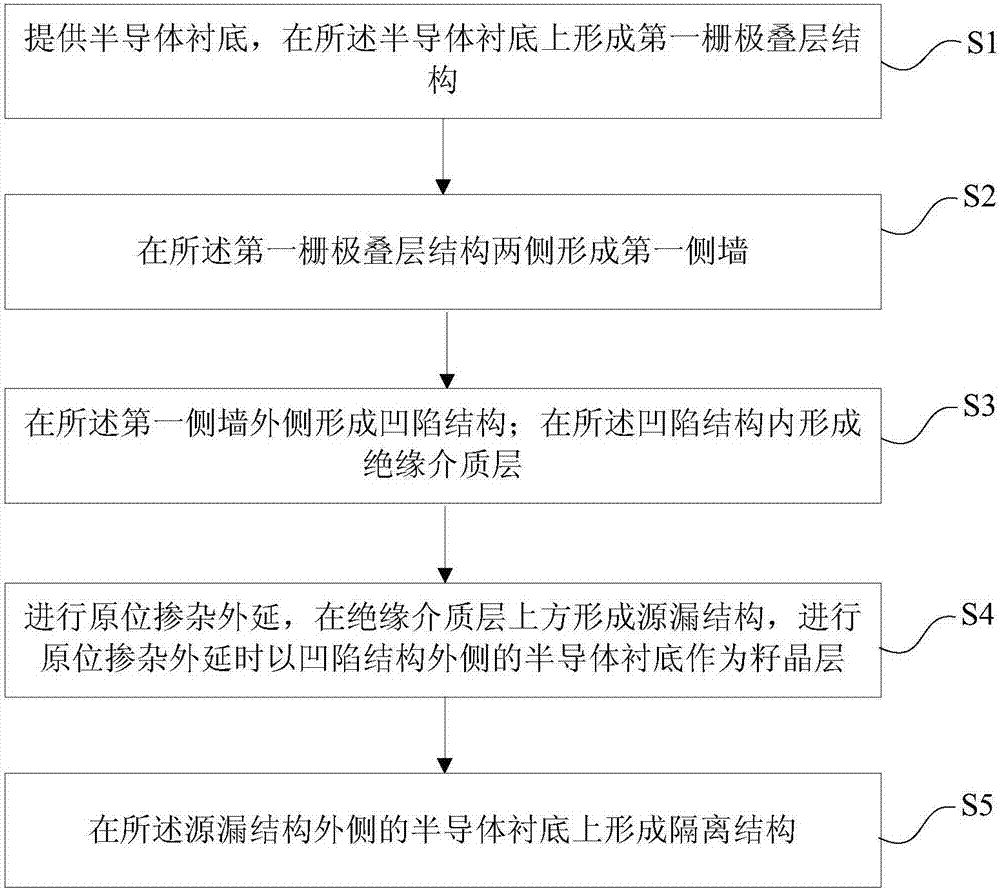

[0075] see Figure 1 to Figure 20 , one embodiment of the present invention provides a kind of preparation method of field effect transistor, the preparation method of described field effect transistor can be suitable for the preparation of quasi-SOI source-drain High K Metal Gate last gate process MOSFET, at least comprises the following steps:

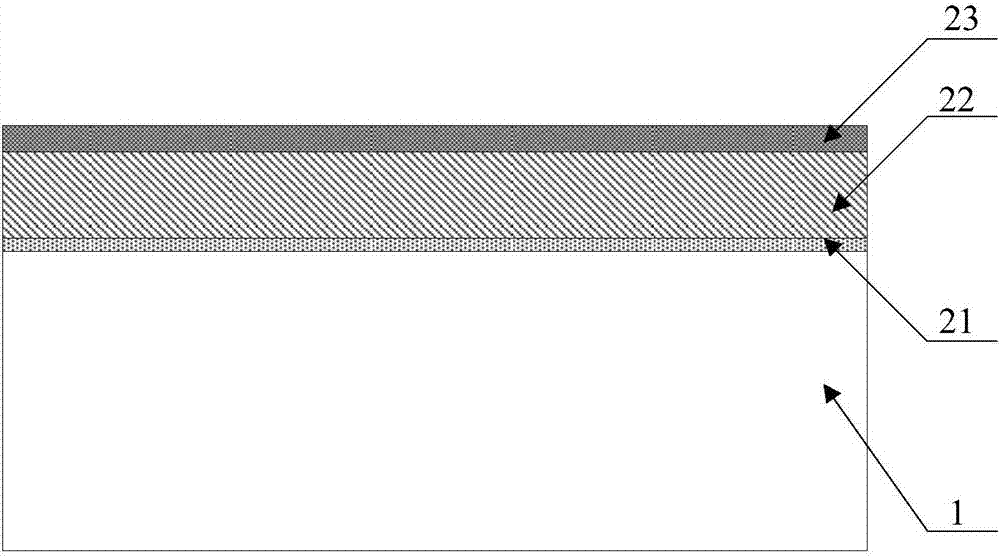

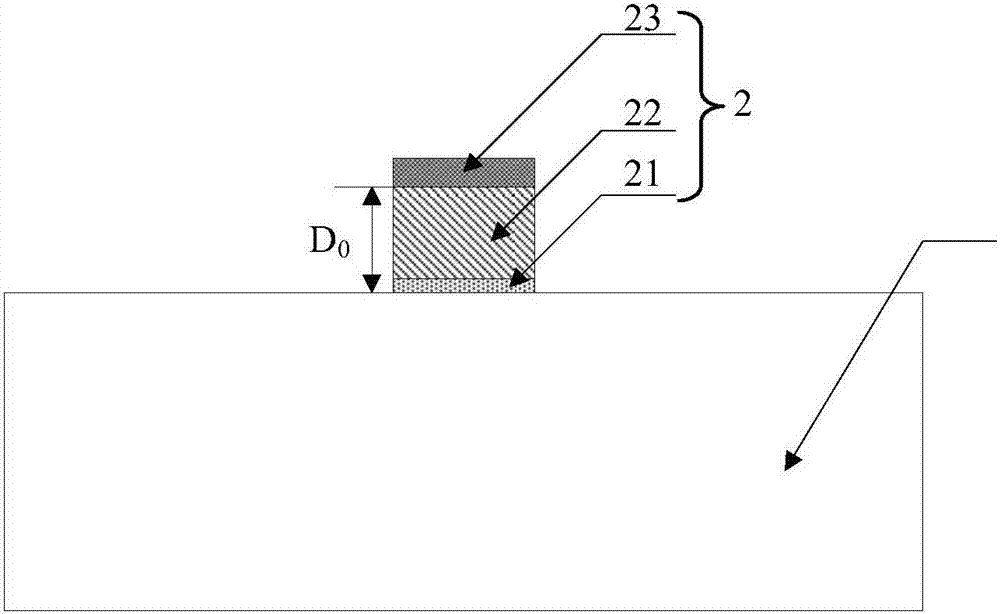

[0076] 1) Provide a semiconductor substrate 1, and form a first gate stack structure 2 on the semiconductor substrate 1; wherein, in the illustrated embodiment, the gate stack structure 2 is a dummy gate, from bottom to top sequentially comprising a gate oxide layer 21, a polysilicon layer 22 and a gate hard mask layer 23;

[0077] 2) forming first spacers 31 on both sides of the first gate stack structure 2;

[0078] 3) forming a recessed structure 4 outside the first sidewall 31; forming an insulating dielectric layer 41 in the recessed structure 4;

[0079] 4) performing in-situ doping epitaxy, forming a source-drain structure 6...

Embodiment 2

[0117] see Figure 21 to Figure 23 , Another embodiment of the present invention provides a kind of preparation method of field effect transistor, the preparation method of described field effect transistor can be suitable for the preparation of quasi-SOI source-drain High K Metal Gate front gate process MOSFET, at least comprises the following steps:

[0118] 1) A semiconductor substrate 1 is provided, and a first gate stack structure 2 is formed on the semiconductor substrate 1 by a gate-front process; wherein in the illustrated embodiment, the first gate stack structure 2 is true Gate, including an oxide interface layer 24, a high dielectric constant layer 25, a work function adjustment layer 26 and a metal gate layer 27 from bottom to top;

[0119] 2) forming first spacers 31 on both sides of the first gate stack structure 2;

[0120] 3) forming a recessed structure 4 outside the first sidewall 31; forming an insulating dielectric layer 41 in the recessed structure 4;

...

Embodiment 3

[0136] see Figure 24 to Figure 26 Another embodiment of the present invention also provides a method for preparing a field effect transistor, which is suitable for the preparation of a quasi-SOI source-drain conventional gate MOSFET, and at least includes the following steps:

[0137] 1) A semiconductor substrate 1 is provided, and a first stacked gate structure 2 is formed on the semiconductor substrate 1 by a conventional process, and the first stacked gate structure 2 includes a gate oxide layer 21, polysilicon layer 22 and gate hard mask layer 23;

[0138] 2) forming first spacers 31 on both sides of the first gate stack structure 2;

[0139] 3) forming a recessed structure 4 outside the first sidewall 31; forming an insulating dielectric layer 41 in the recessed structure 4;

[0140] 4) performing in-situ doping epitaxy, forming a source-drain structure 61 above the insulating dielectric layer 41, and using the semiconductor substrate 1 outside the recessed structure 4...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com