High-performance and high-integration-level L-shaped gate-control schottky barrier tunneling transistor

A tunneling transistor, a high-integration technology, applied in semiconductor devices, electrical components, circuits, etc., can solve the problem of weakening the electric field distribution and carrier distribution control ability of the gate to the source region and drain region, and forming Schottky potential Barrier difficulties, difficult to practical Schottky barrier MOSFETs transistors and other issues, to achieve excellent current conduction ability, improve sub-threshold characteristics and conduction ability, good reverse characteristics and static characteristics

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

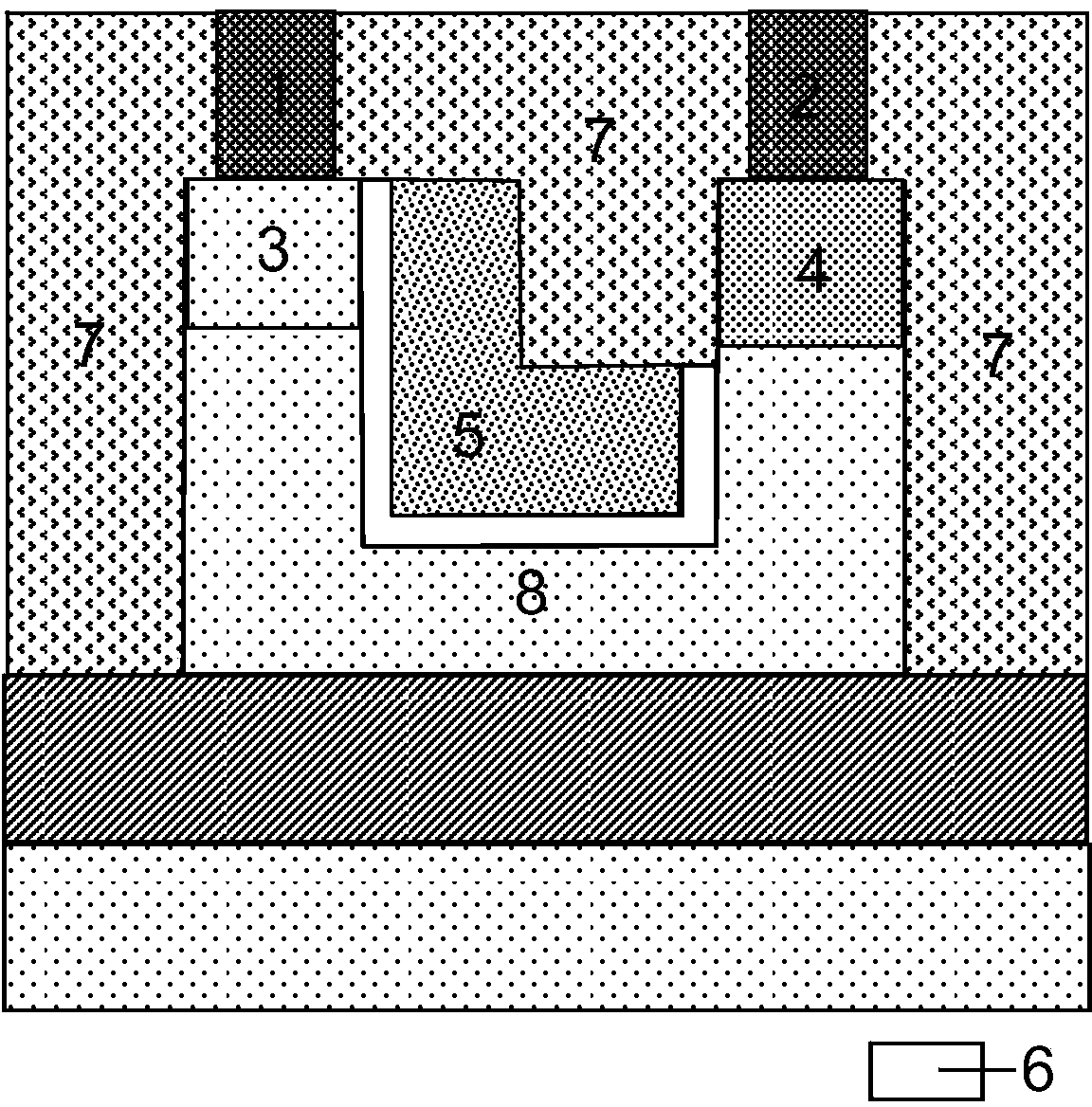

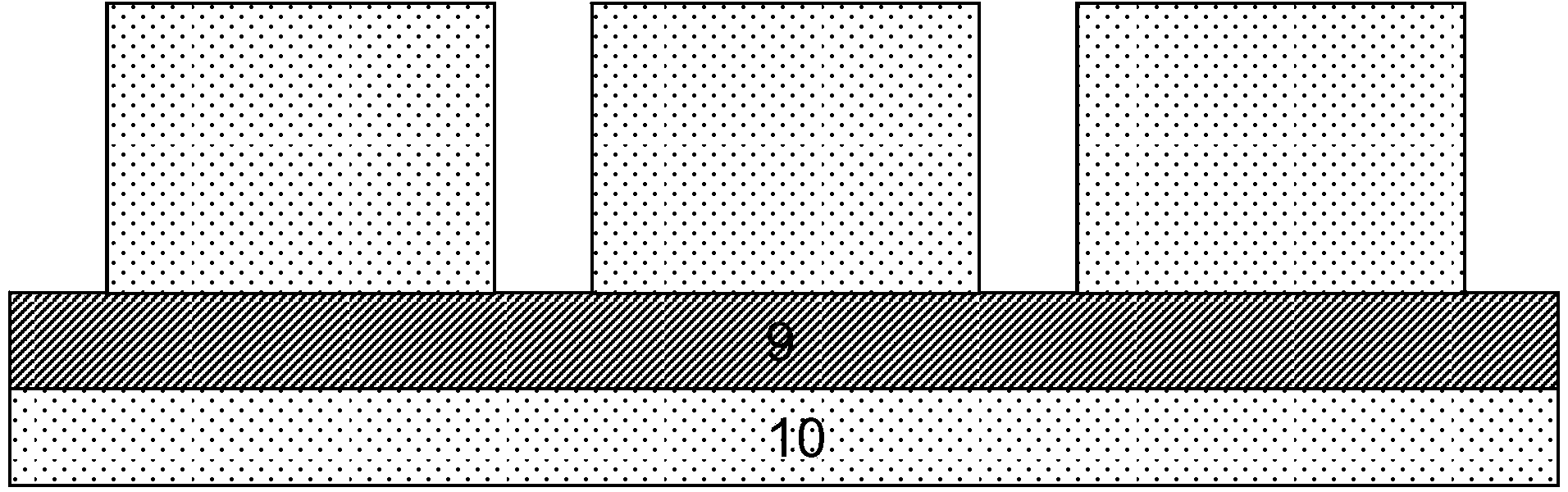

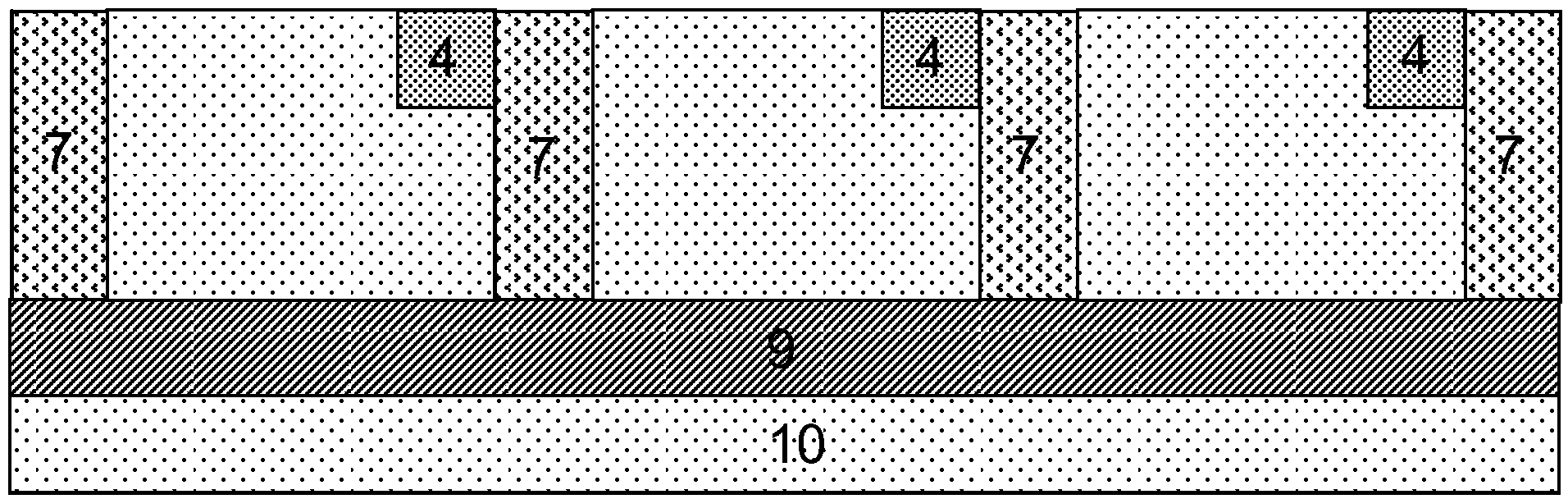

[0033] The invention provides an L-shaped gate-controlled Schottky barrier tunneling transistor with high performance and high integration, without introducing compound semiconductor, silicon germanium or germanium and other materials with narrower band gap than silicon as the tunneling part of the device , but use the Schottky contact barrier formed between the source electrode and the undoped intrinsic silicon source region as the tunneling barrier of the device, and the Schottky barrier height is smaller than the silicon band gap, so The fact that the carrier tunneling probability is higher than the tunneling probability between the conduction band and the valence band of silicon can improve the conductivity of the tunneling transistor, and the gate electrode with the capital letter L is used as the switch control electrode of the device. , on the one hand, the Schottky barrier width of the intrinsic silicon source region is controlled by changing the gate electrode voltage,...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com