Low-temperature polycrystalline silicon thin film transistor, manufacturing method thereof and display device

A thin-film transistor, low-temperature polysilicon technology, applied in transistors, semiconductor/solid-state device manufacturing, electrical solid-state devices, etc., can solve the problems of long diffusion distance, long time, long heat treatment time, etc., and achieve shortened distance and reduced time. , The effect of reducing process cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

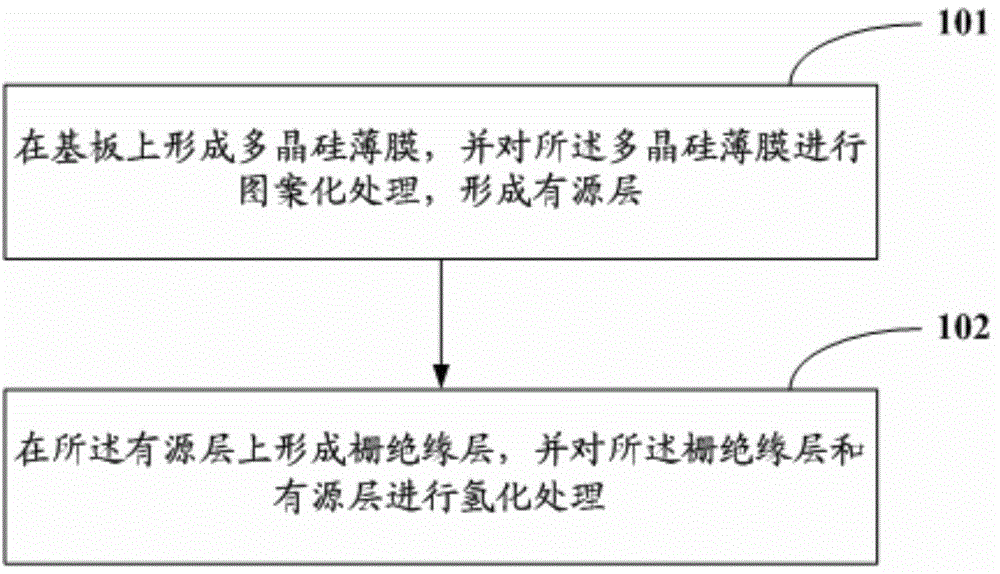

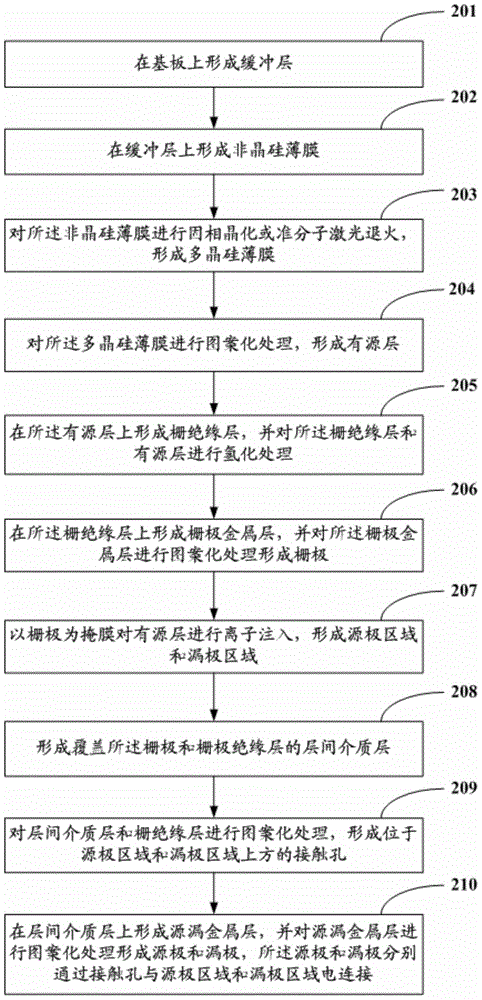

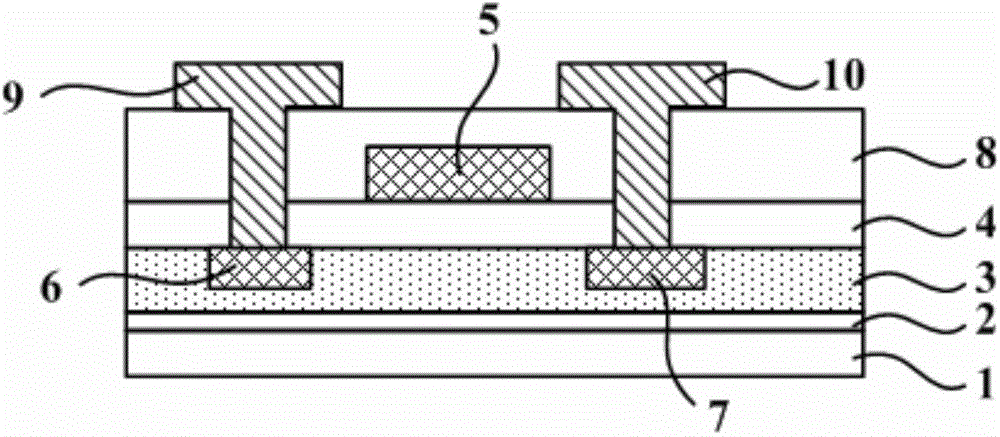

[0037] In order to solve the technical problem of long hydrogenation treatment time in the manufacturing process of the thin film transistor in the prior art, the present invention provides a low-temperature polysilicon thin film transistor, a manufacturing method thereof, and a display device. In this technical solution, after the gate insulating layer is fabricated, the gate insulating layer and the active layer are directly hydrogenated, and the hydrogen only needs to pass through the gate insulating layer to reach the interface between the gate insulating layer and the active layer to passivate the dangling bonds. and repair the grain boundary defects of the active layer, which greatly shortens the distance of hydrogen diffusion, reduces the time of the hydrogenation process, and thus greatly reduces the process cost of the thin film transistor. In order to make the purpose, technical solution and advantages of the present invention clearer, the following specific examples ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com