Method for forming metal gate

A metal gate and dummy gate technology, used in electrical components, semiconductor/solid-state device manufacturing, semiconductor devices, etc., can solve problems such as affecting the stability of transistors and changing the thickness of the interface material layer.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

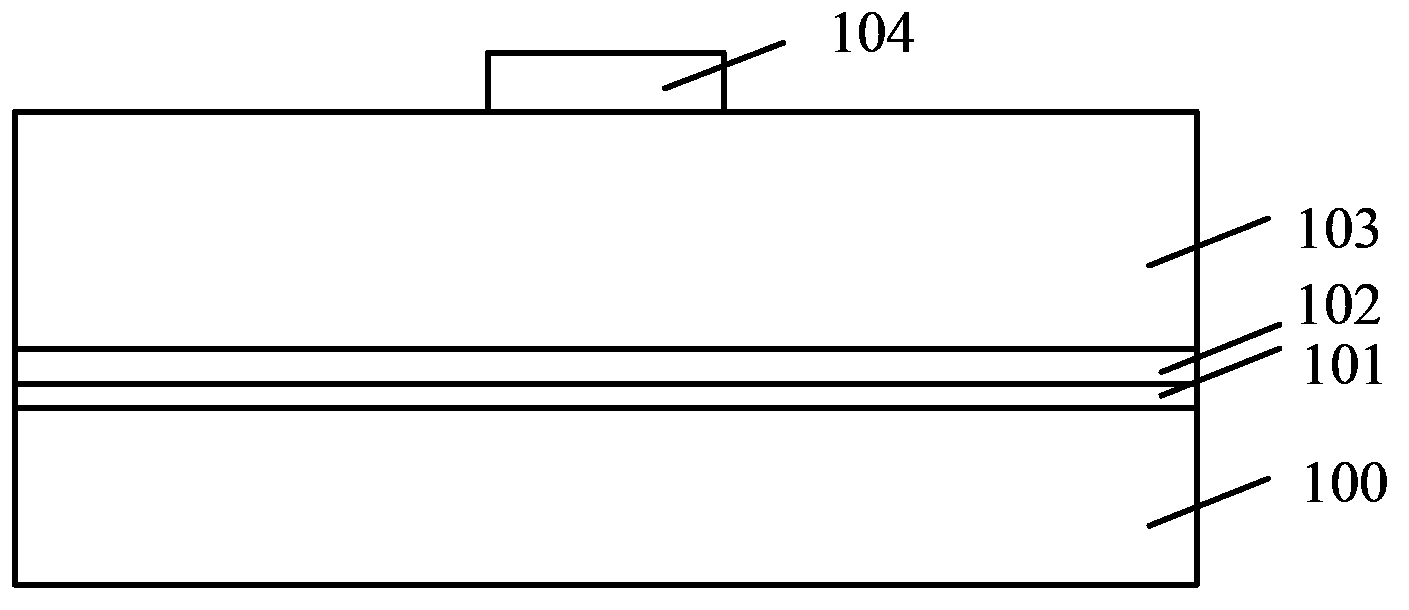

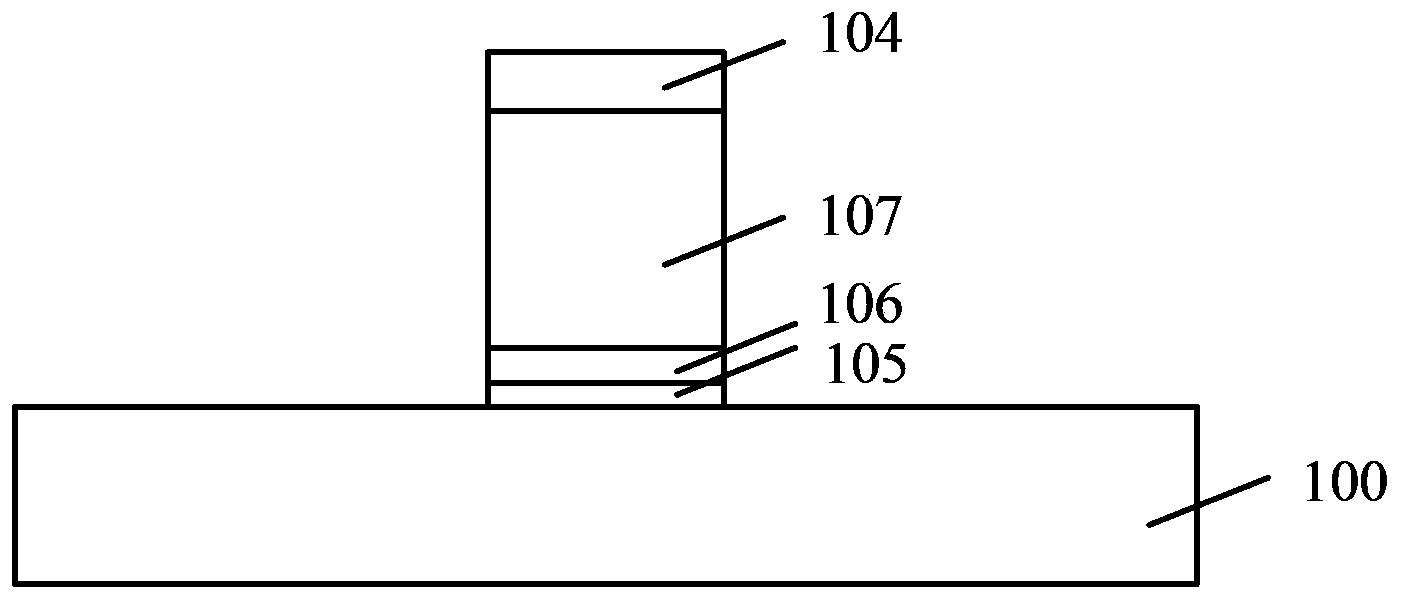

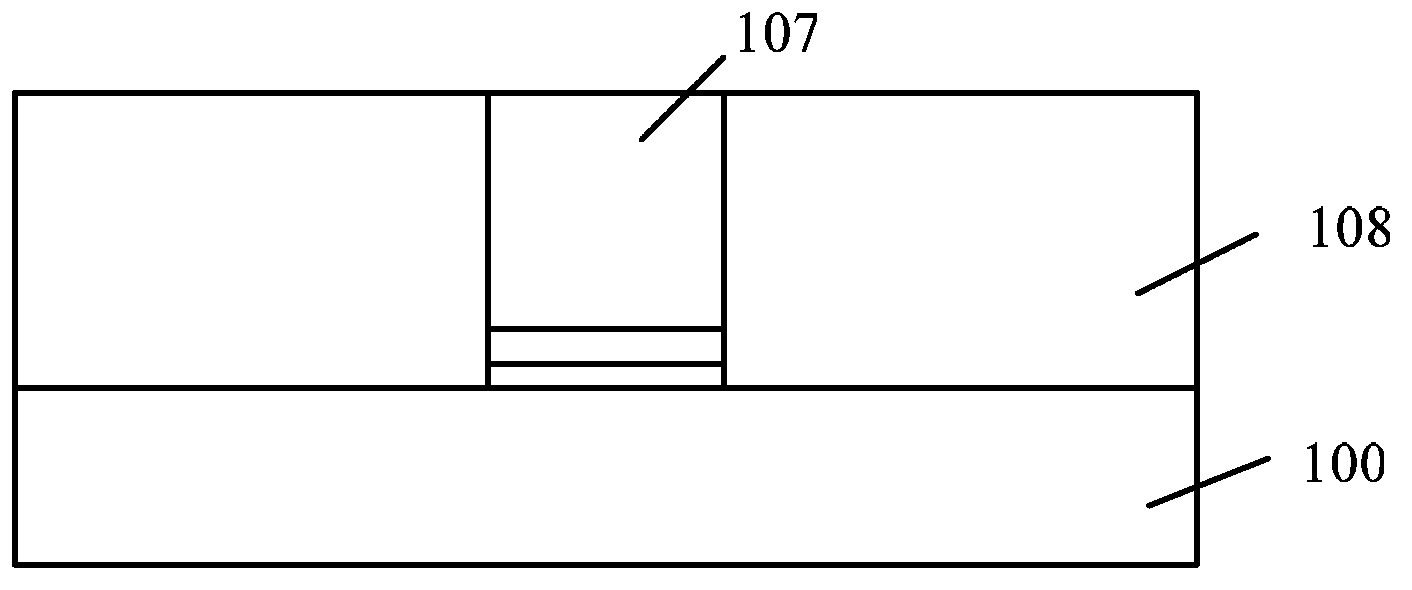

[0029] The inventors found that in the prior art, when making metal gates, the thickness of the interface layer finally formed is always thicker than the thickness of the interface material layer, so that the actual thickness of the interface layer deviates from the designed thickness of the interface layer, which affects the performance of the transistor. performance and stability.

[0030] The inventors have further studied and found that the existing interface material layer is usually formed by a thermal oxidation process. After the interface material layer is formed, the polysilicon layer, hard mask layer, dielectric layer, etc. are all formed by chemical vapor deposition. Chemical vapor deposition During the process, the temperature of the deposition chamber is relatively high (500-800 degrees Celsius). In a high-temperature environment, some oxygen elements will pass through the polysilicon layer and the hard mask layer to reach the surface of the semiconductor substrate...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com