Electrostatic discharge protection circuit

An electrostatic discharge protection and circuit technology, which is applied to emergency protection circuit devices, emergency protection circuit devices for limiting overcurrent/overvoltage, circuits, etc., can solve the problems of occupying layout area, increase efficiency and reduce capacitance The effect of load

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Method used

Image

Examples

Embodiment Construction

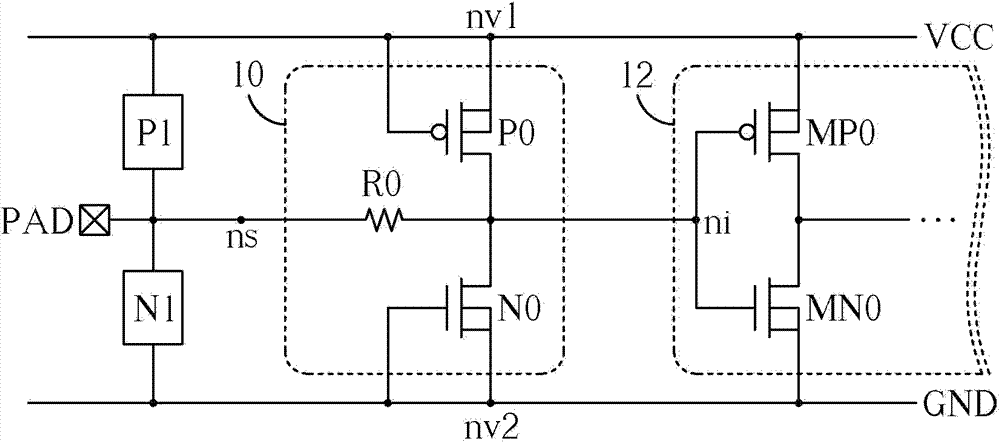

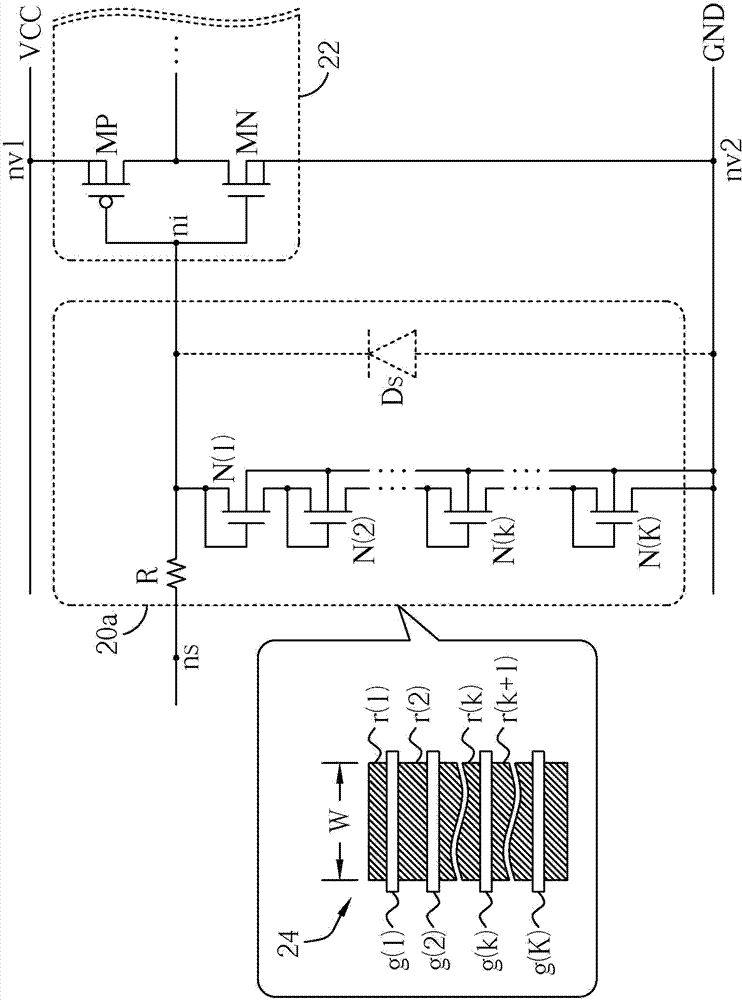

[0028] Please refer to figure 2 , which shows an electrostatic discharge protection circuit 20a according to an embodiment of the present invention, which can be disposed in a chip to protect the internal circuit 22 in the chip. For example, the internal circuit 22 may include a transistor MP and a transistor MN, which are n-channel and p-channel metal-oxide-semiconductor transistors respectively. (signal node) on the signal winding to receive the signal. The signal source can come from an input pad, or be coupled to node ns by a signal output from a different power domain. The internal circuit 22 is respectively coupled to the voltage VCC (power supply voltage) and GND (ground voltage) by the power windings of the nodes nv1 and nv2 (the two nodes can be regarded as voltage nodes); the source and bulk of the transistor MN are It is coupled to the node nv2, and the source and body of the transistor MP are coupled to the node nv1. Transistors MN and MP can be thin-oxide tran...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com