Integrated circuit structure

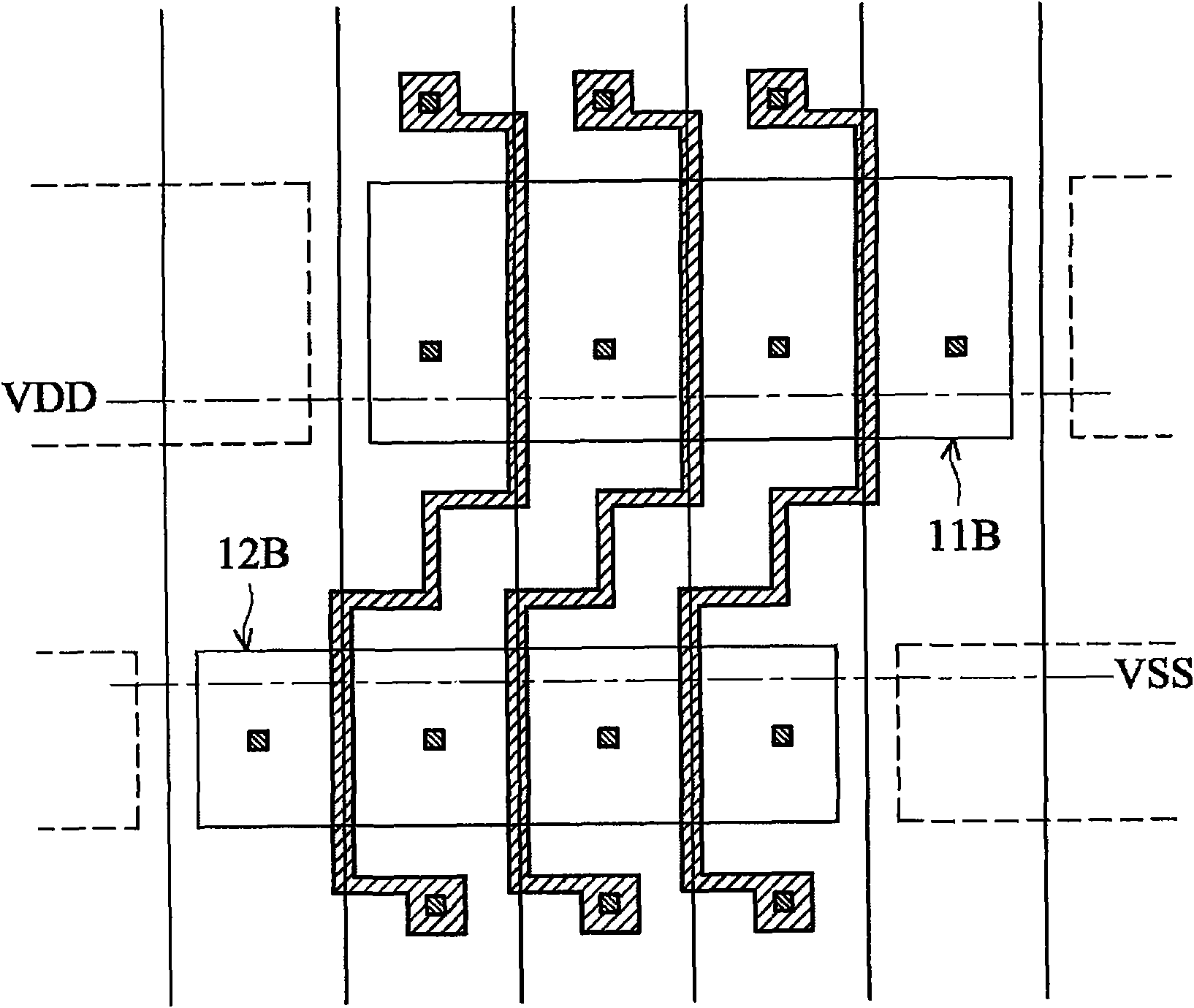

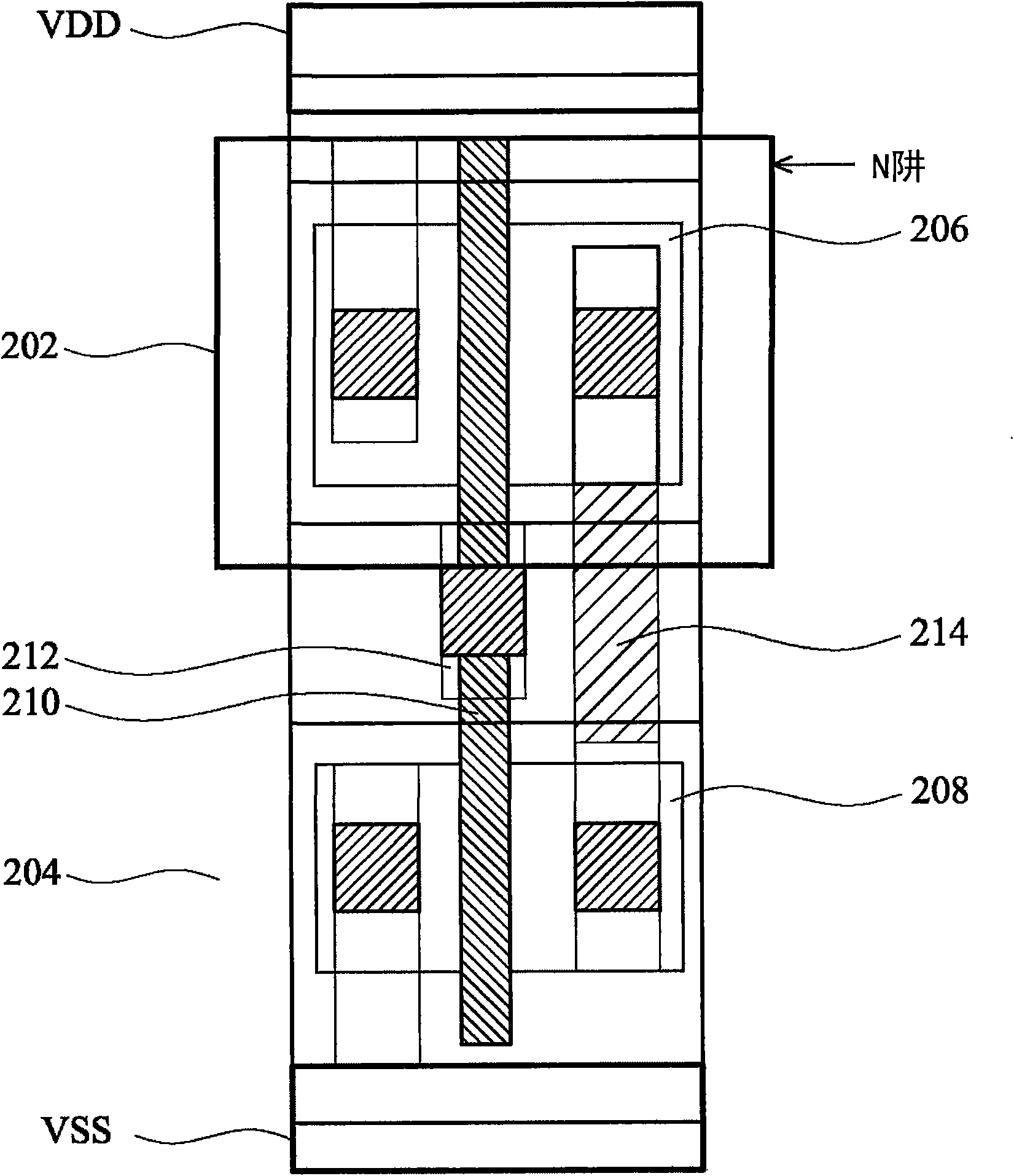

By arranging the internal connection points outside the metal oxide semiconductor area in the integrated circuit, and using generally straight gate electrode wires and vertically overlapping power supply wires, the line width uniformity and third problems caused by the distortion of polysilicon wires in the integrated circuit are solved. The utilization rate of the second metallization layer improves layout efficiency and flexibility.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

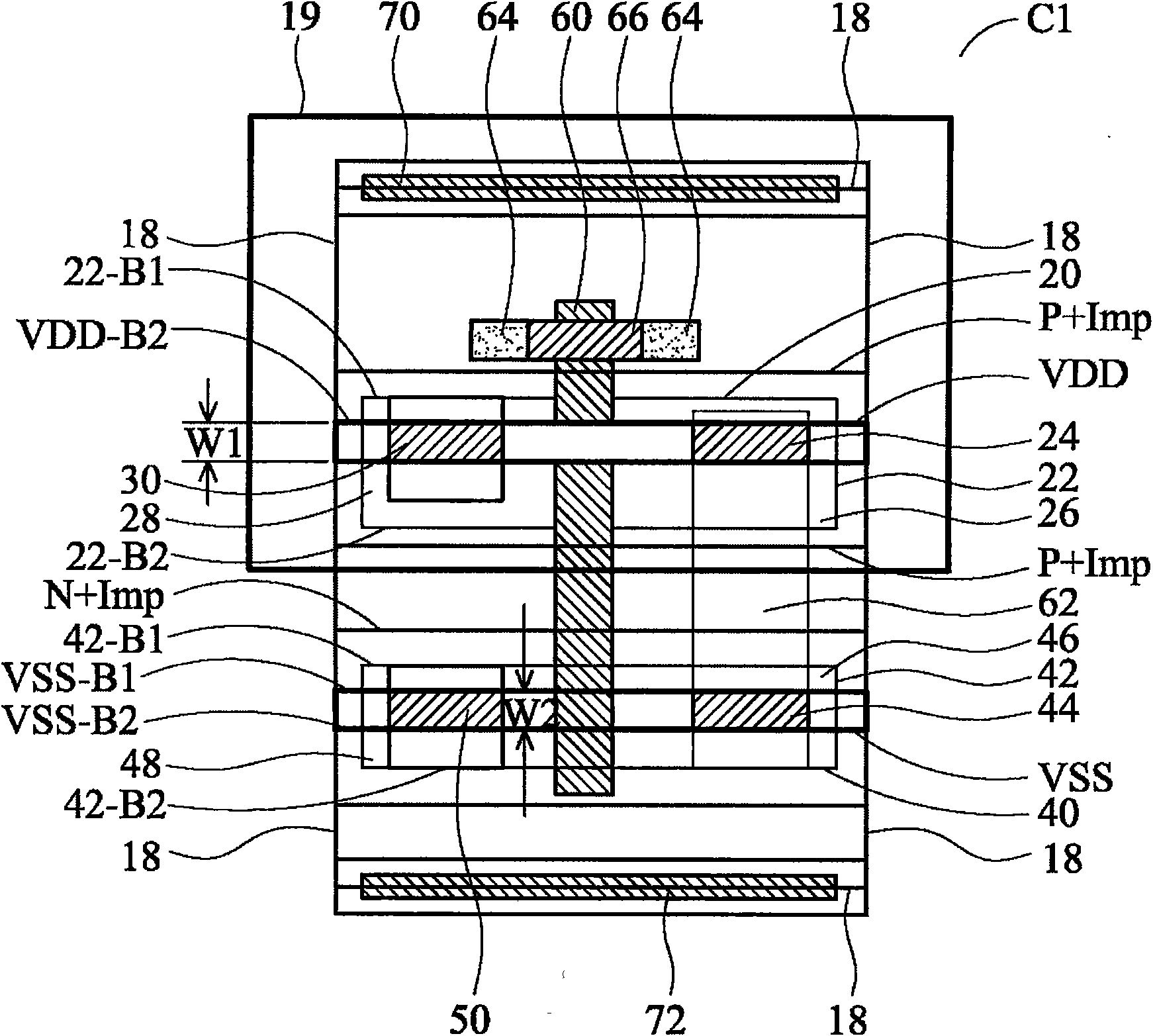

[0073] The present invention provides a novel layout method of standard cells and its final layout situation. And discuss the differences through different embodiments. In the case of illustration in different figures of the present invention, the same reference numerals represent the same elements. In the following, descriptions such as "horizontal" and "horizontally" indicate that the circuit of the present invention is arranged in a direction parallel to the surface of the chip, while descriptions such as "vertical" and "vertically" indicate that it is perpendicular to the surface of the chip. The orientation of the surface.

[0074] figure 2 An embodiment according to the invention is shown, in which a part of cell C1 is shown. Cell C1 may be stored in a cell library, an I / O cell, an embedded cell, a Dynamic Random Access Memory (DRAM) cell, a Static Random Access Memory (SRAM) cell, a hybrid Part of a standard unit of a signal circuit unit or the like. The border of...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com