LDO circuit using bidirectional asymmetry buffer structure to improve performance

A buffer and asymmetric technology, applied in the direction of instruments, adjusting electrical variables, control/regulation systems, etc., can solve the problems of reducing LDO power supply voltage rejection ratio, increasing LDO quiescent current, increasing circuit complexity, etc., to improve transient Response performance, expansion of unity gain bandwidth, flexible circuit configuration and various effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

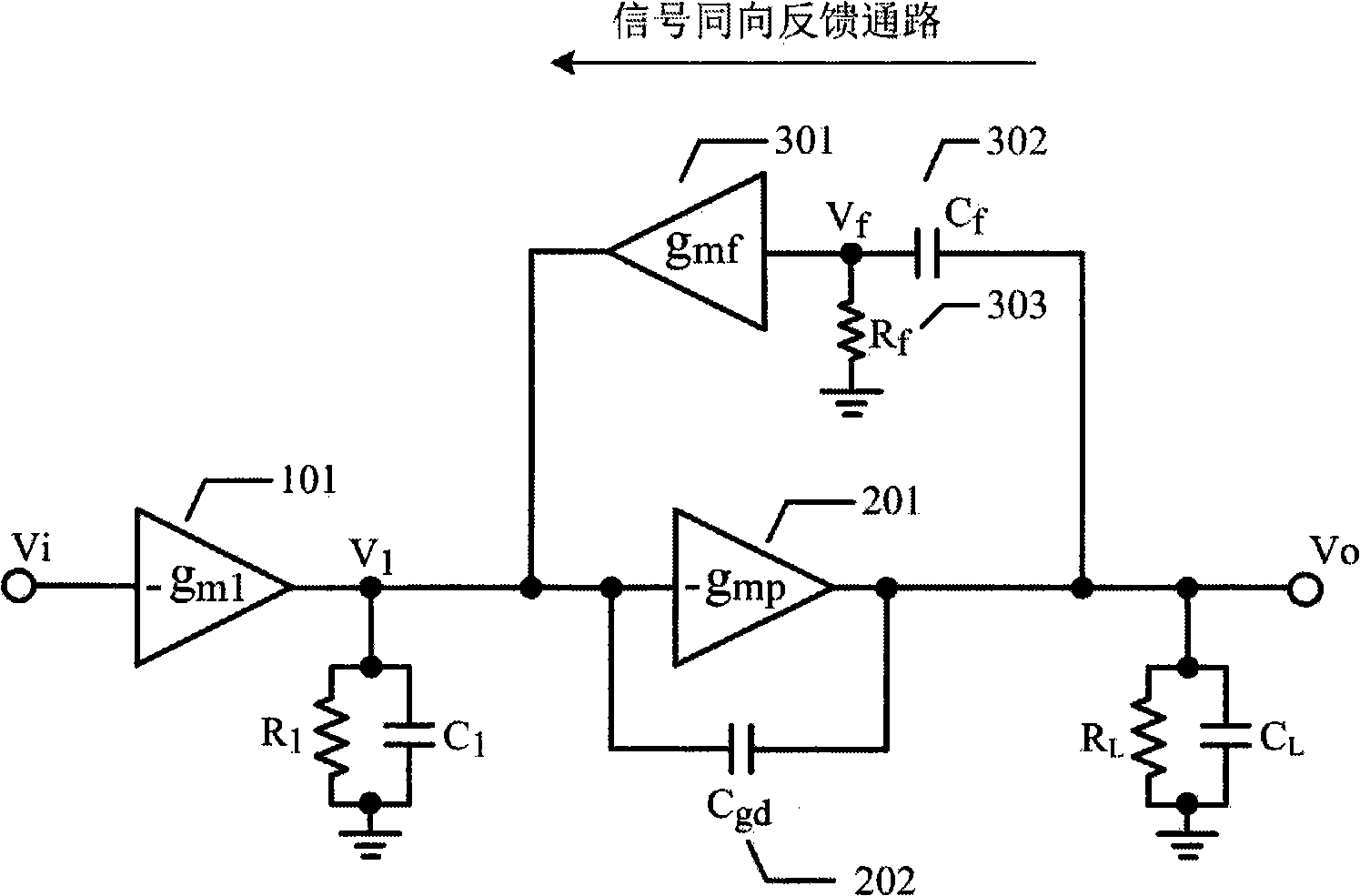

[0047] Figure 5 A block diagram of the circuit for canceling the right-half-plane zero point of the present invention is given, including the buffer stage 401, the first inverse gain stage 101, the LDO transfer element 201, and the gate-to-drain parasitic capacitance C of the LDO transfer element 201 gd 202, and by the second inverting gain stage 301, capacitor C f 302, resistance R f 303 bidirectional asymmetric buffer structure. Node V i , V b , V 2 and V o are respectively the input end of the buffer stage 401, the output end, the output end of the first inverting gain stage 101, and the output end of the LDO, R b 、C b for node V b The output impedance and lumped parasitic capacitance, R 2 、C 2 for node V 2 The output impedance and lumped parasitic capacitance, R L 、C L for node V o output impedance (including load impedance) and load capacitance.

[0048] It should be noted, Figure 5 The buffer stage 401 in the shown functional block diagram may be a b...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com