Semiconductor device and method for manufacturing the same

a technology of semiconductor devices and semiconductors, applied in semiconductor devices, electrical devices, transistors, etc., can solve the problems of low on-resistance or the like, high cost, and low efficiency, and achieve the effect of effectively preventing the drop of breakdown voltage around the cell region

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

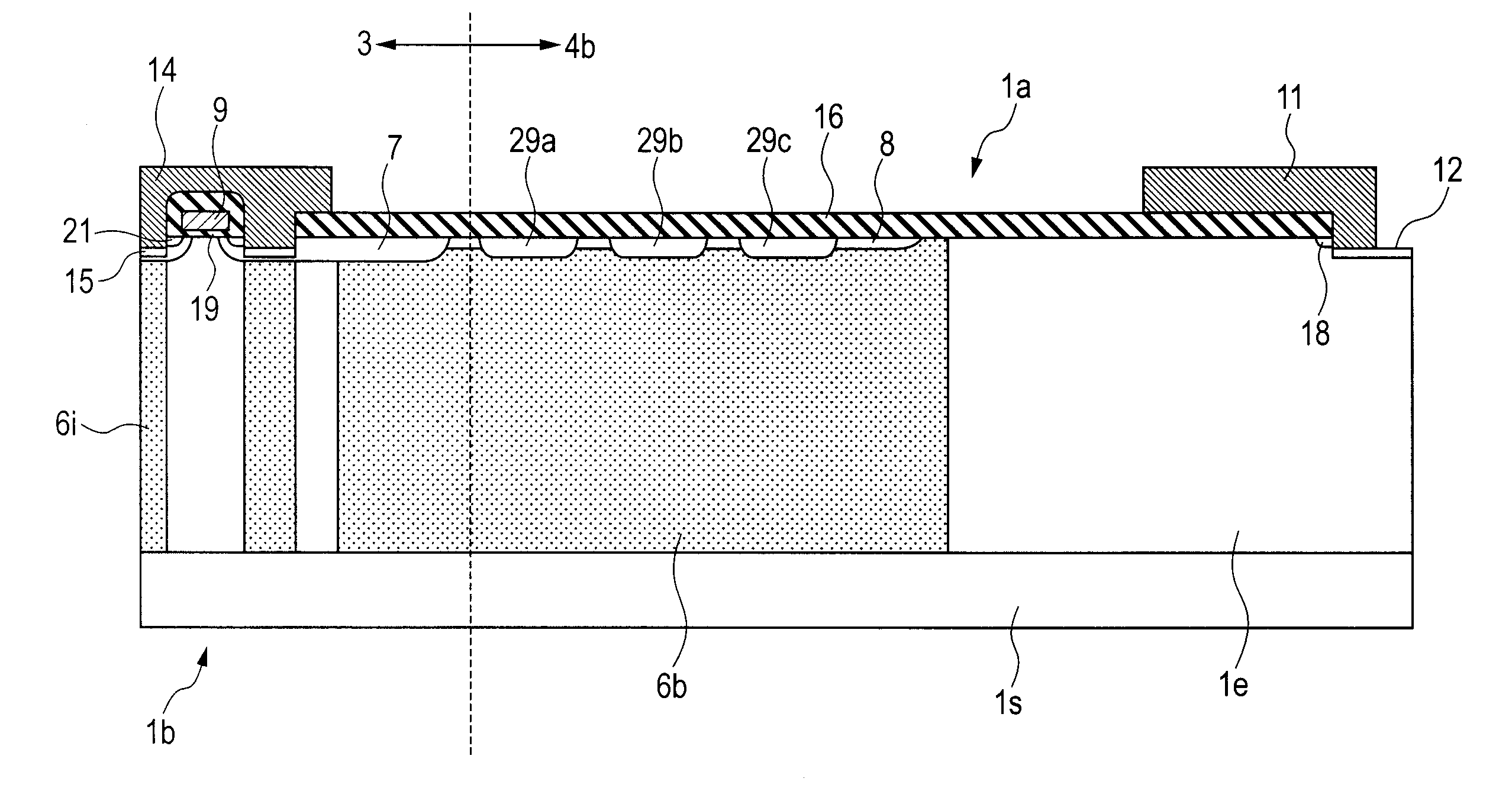

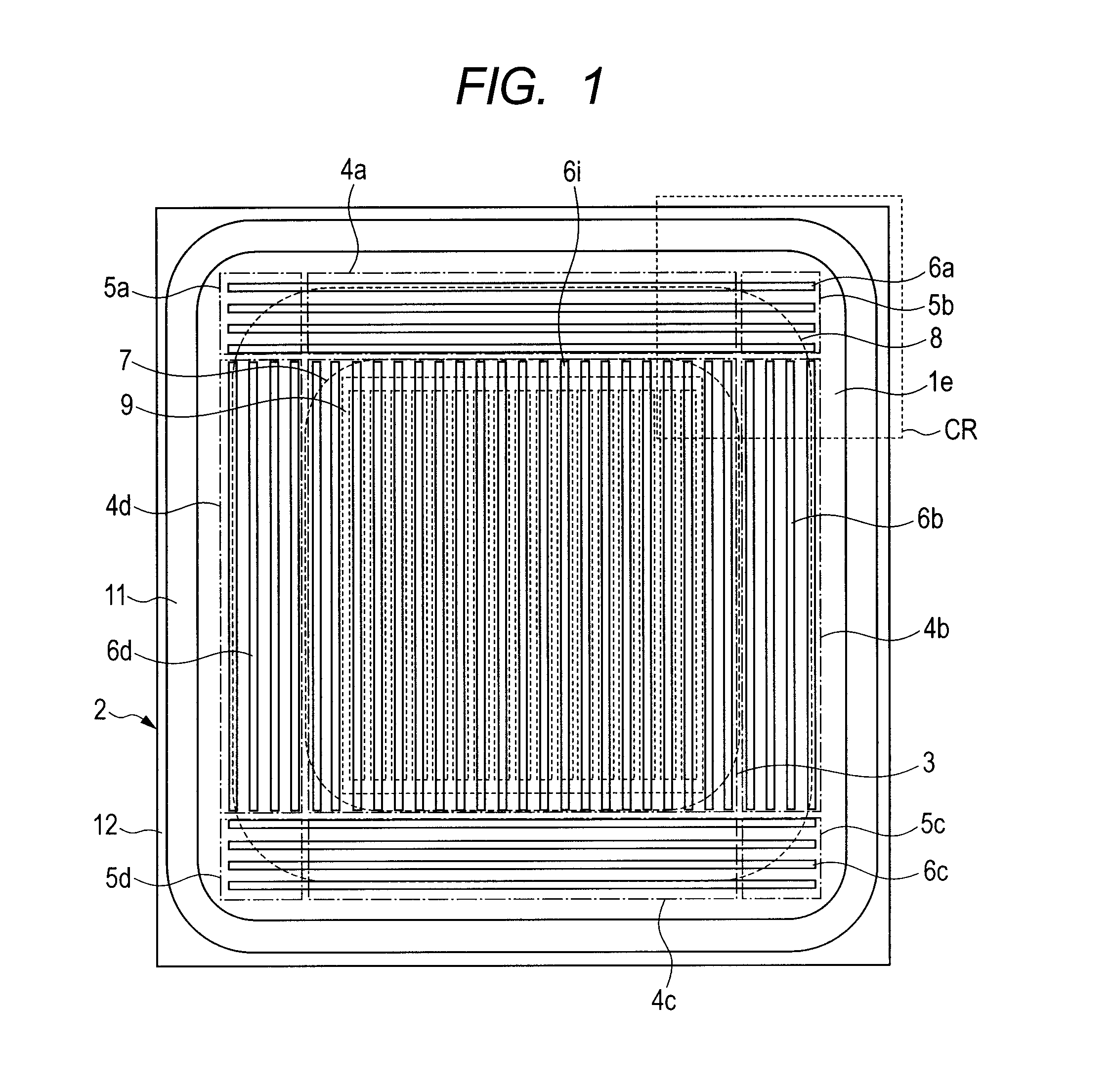

1. Description of the device structure (2D resurf structure) of a power MOSFET as a semiconductor device according to the invention (see mainly FIGS. 1 to 4).

[0059]Although the super junction structure is also a kind of resurf structure, the resurf structure described in this section is the resurf structure for a P− type surface layer formed over a bulk super junction structure surface of the bulk in a cell peripheral region. In the cell peripheral region, P type columns extend parallel to corresponding sides of the cell region, and in terms of the degree of freedom in electric field directions in the depletion layer extending to the P− type surface layer, the structure also has a 2-degree-of-freedom, specifically the direction from the back surface of the substrate to its front surface and the direction from a chip edge toward the inside of the device main surface; thus this type of resurf structure is called a 2D resurf structure.

[0060]Next, the function of the 2D resurf structure...

second embodiment

3. Description of the device structure (3D resurf structure) of a power MOSFET as a semiconductor device according to the invention (see mainly FIGS. 19 to 21)

[0082]In the resurf structure described in this section, P type columns extend perpendicularly to corresponding sides of the cell region in the cell peripheral region, so in terms of the degree of freedom in electric field directions in the depletion layer extending to the P− type surface layer, the structure has a 3-degree-of-freedom, specifically the direction parallel to a corresponding side of the cell region, the direction from the back surface of the substrate to its front surface, and the direction from the chip edge toward the inside of the device main surface; thus this type of resurf structure is called a 3D resurf structure. The basic configuration of the device is almost the same as that of the device described in Section 1 and basically, only aspects which are different from it will be described in this and subseq...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com