Lead mfg. method and method for shortening distance between lead an pattern

A technology of wire spacing and manufacturing method, which is applied in the manufacture of wires and narrows the distance between wires and patterns. It can solve problems such as deviation, inoperability of components, and decline in the overall performance and reliability of semiconductor components, so as to reduce the size of components and shrink the line width. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

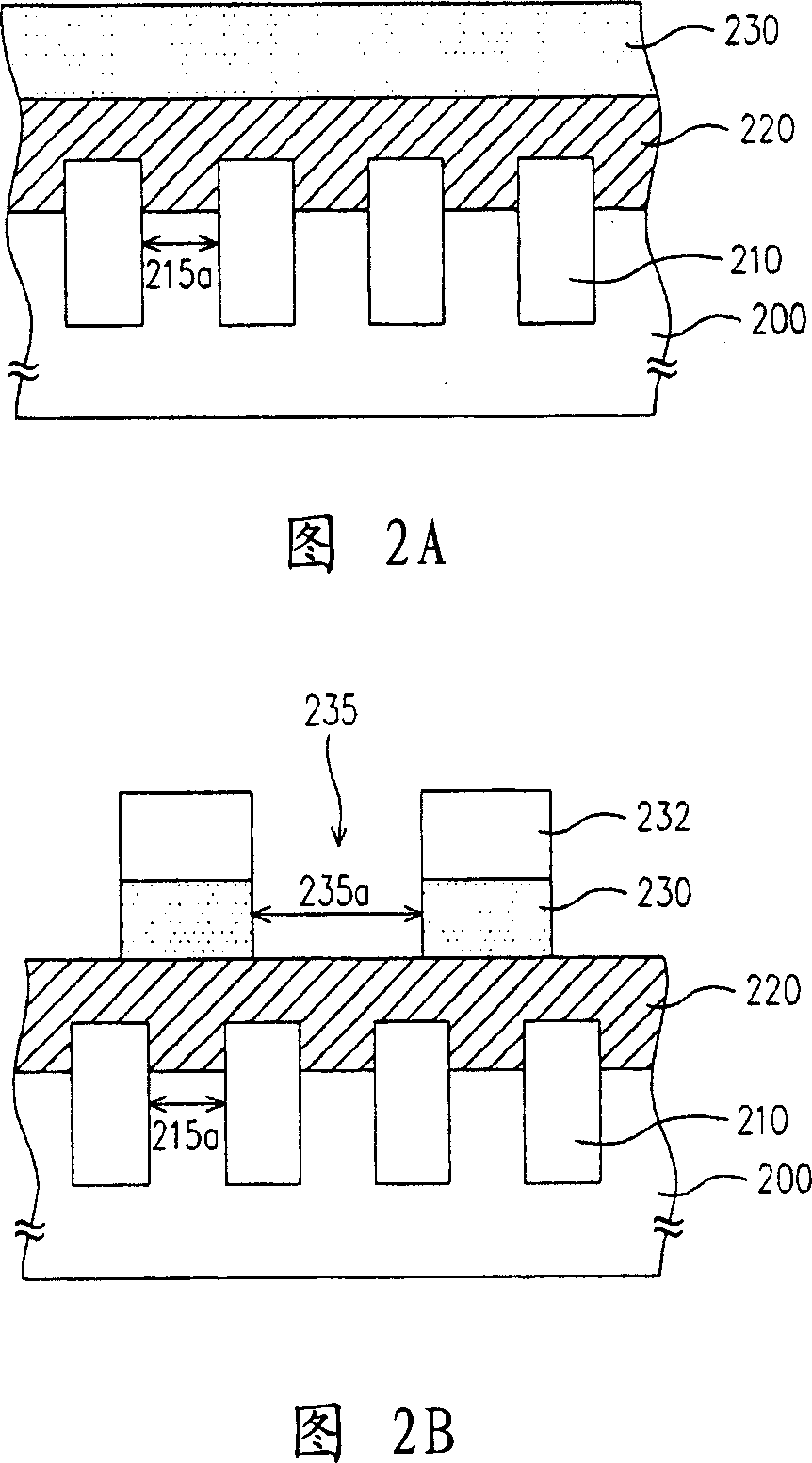

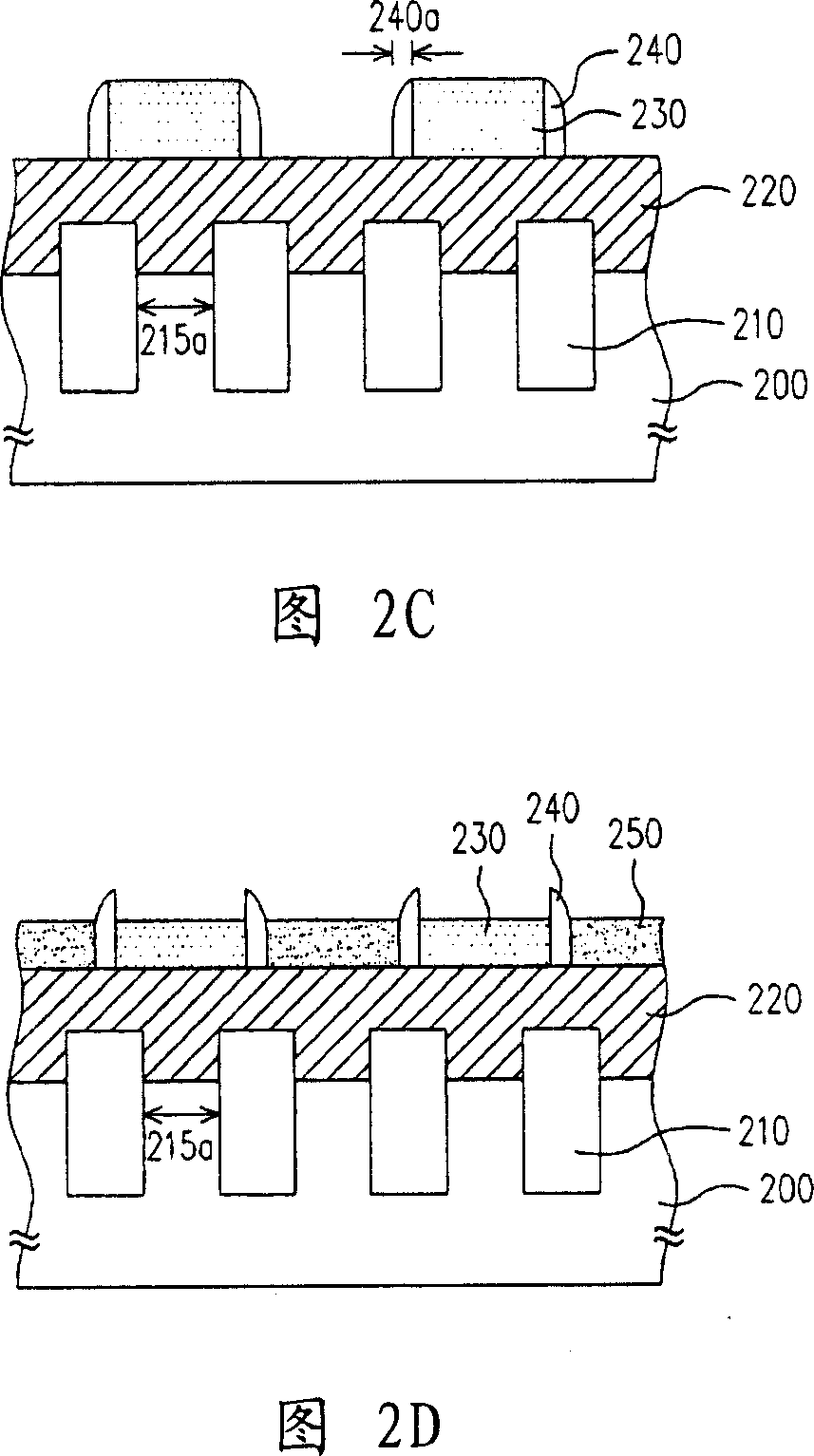

[0041] 2A to 2E are cross-sectional views illustrating a manufacturing process of a wire according to an embodiment of the present invention.

[0042] Referring to FIG. 2A , this embodiment is described by taking the formation of word lines of a memory as an example. Firstly, a substrate 200 having at least a plurality of isolation structures 210 is provided, and the surface of the substrate 200 may further include a dielectric layer (not shown). The isolation structure 210 is, for example, shallow trench isolation. According to the resolution of currently used photolithography machines, the width 215 a between the isolation structures 210 is, for example, 90 nm. Then, a layer 220 to be etched is formed on the substrate 200 . The layer to be etched 220 is, for example, a conductive layer, which is used as a subsequent control gate or wire. The material of the to-be-etched layer 220 is, for example, a conductive material such as doped polysilicon, metal or metal silicide, an...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com